领航者ZYNQ之FPGA开发指南高清.pdf

http://www.100md.com

2020年11月23日

|

| 第1页 |

|

| 第6页 |

|

| 第12页 |

|

| 第21页 |

|

| 第36页 |

|

| 第534页 |

参见附件(28819KB,544页)。

正点原子领航者FPGA开发指南参考书籍

FPGA 器件属于专用集成电路中的一种半定制电路,是可编程的逻辑列阵,能够有效的解决原有的器件门电路数较少的问题。FPGA 的基本结构包括可编程输入输出单元,可配置逻辑块,数字时钟管理模块,嵌入式块RAM,布线资源,内嵌专用硬核,底层内嵌功能单元。

图片预览

内容简介

领航者ZYNQ之FPGA开发指南将由浅入深的带领大家开启ZYNQ的学习之旅。本手册主要学习ZYNQ的 PL(Program Logic,可编程逻辑)部分,共分为硬件篇、软件篇、语法篇与实战篇共四个篇章。

硬件篇:硬件篇主要介绍本手册的硬件实验平台以及硬件资源详解。

软件篇:软件篇主要介绍 FPGA 常用开发软件的安装教程与使用方法。

语法篇:语法篇主要介绍 FPGA 的硬件描述语言 Verilog 的语法知识。

实战篇:实战篇主要通过 21 个实例带领大家一步步深入了解 FPGA。

本手册为领航者 ZYNQ 开发板的配套教程,在开发板配套的光盘里面,有开发板的原理图以及所有实例的完整代码,这些代码都有详细的注释,所有源码都经过我们严格测试,不会有任何编译错误。另外,源代码有我们生成好的 bit 文件(用于程序的文件),大家只需要通过器到开发板即可看到实验现象,亲自体验实验过程。

本手册不仅非常适合广大学生和电子爱好者学习 FPGA,其大量的实验以及详细的注释,也是公司产品开发的不二参考。

目录大全

内容简介 .............................................................................. 9

前 言 .............................................................................. 10

第一篇 硬件篇 ................................................................... 11

ZYNQ简介 ................................................................. 12

ZYNQ简介 ..................................................................... 13

FPGA简介 ..................................................................... 15

ZYNQ PL简介 .................................................................. 20

ZYNQ PS简介 .................................................................. 26

实验平台简介 ............................................................. 31

领航者ZYNQ开发板资源初探 ........................... ......

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

1

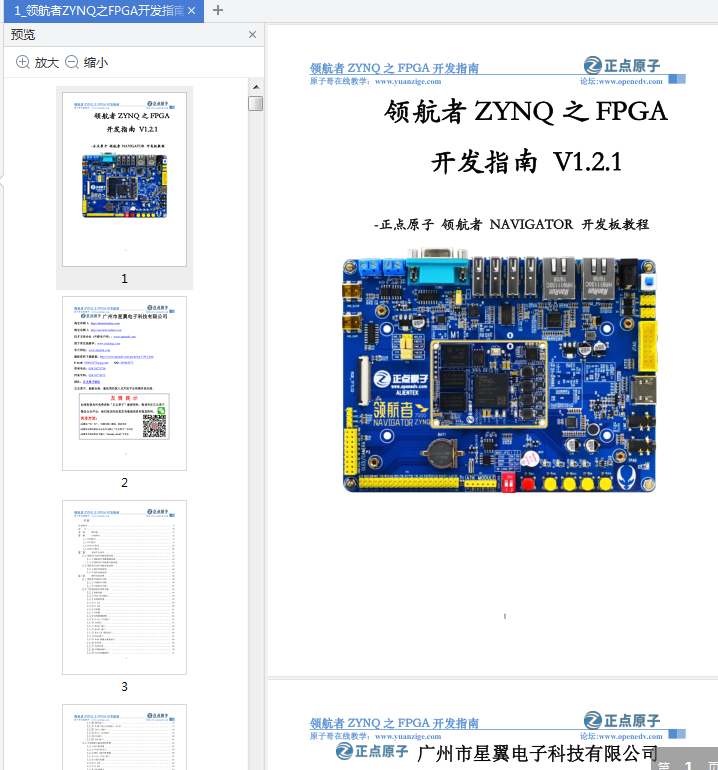

领航者ZYNQ之FPGA 开发指南

领航者 ZYNQ 之 FPGA

开发指南 V1.2.1

-正点原子 领航者 NAVIGATOR 开发板教程

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

2

领航者ZYNQ之FPGA 开发指南

广州市星翼电子科技有限公司

淘宝店铺1:http:eboard.taobao.com

淘宝店铺2:http:openedv.taobao.com

技术支持论坛 (开源电子网) :www.openedv.com

原子哥在线教学:www.yuanzige.com

官方网站:www.alientek.com

最新资料下载链接:http:www.openedv.compostslist13912.htm

E-mail: 389063473@qq.com QQ: 389063473

咨询电话:020-38271790

传真号码:020-36773971

团队:正点原子团队

正点原子,做最全面、最优秀的嵌入式开发平台软硬件供应商。

友 情 提 示

如果您想及时免费获取“正点原子”最新资料,敬请关注正点原子

微信公众平台,我们将及时给您发布最新消息和重要资料。

关注方法:

(1)微信“扫一扫”,扫描右侧二维码,添加关注

(2)微信→添加朋友→公众号→输入“正点原子”→关注

(3)微信→添加朋友→输入“alientek_stm32” →关注

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

3

领航者ZYNQ之FPGA 开发指南

目录

内容简介 .............................................................................. 9

前 言 .............................................................................. 10

第一篇 硬件篇 ................................................................... 11

ZYNQ简介 ................................................................. 12

ZYNQ简介 ..................................................................... 13

FPGA简介 ..................................................................... 15

ZYNQ PL简介 .................................................................. 20

ZYNQ PS简介 .................................................................. 26

实验平台简介 ............................................................. 31

领航者ZYNQ开发板资源初探 ..................................................... 32

领航者开发板底板资源 ................................................... 32

领航者开发板核心板资源 ................................................. 34

领航者ZYNQ开发板资源说明 ..................................................... 36

硬件资源说明 ........................................................... 36

软件资源说明 ........................................................... 42

硬件资源详解 ............................................................. 45

领航者ZYNQ的IO分配 ........................................................... 46

PL端的IO分配 ........................................................... 46

PS端的IO分配 ........................................................... 51

开发板底板原理图详解 ......................................................... 56

底板电源 ............................................................... 56

ZYNQ 启动模式 .......................................................... 59

有源蜂鸣器 ............................................................. 59

PL LED ................................................................. 60

PS LED ................................................................. 60

PL按键 ................................................................. 61

PS按键 ................................................................. 61

电容触摸按键 ........................................................... 62

14-Pin JTAG接口 ........................................................ 63

USB串口 ............................................................... 63

RS232 接口 ............................................................ 64

RS485 接口 ............................................................ 65

RGB LCD 模块接口....................................................... 66

XADC接口 .............................................................. 67

OLED摄像头模块接口 ................................................... 68

EEPROM ................................................................ 68

实时时钟 .............................................................. 69

ATK模块接口 ............................................................ 70

I2S音频编解码 ......................................................... 71

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

4

领航者ZYNQ之FPGA 开发指南

HDMI接口 .............................................................. 72

PL端千兆以太网接口(RJ45) ............................................. 74

USB 2.0接口 ........................................................... 76

Micro SD卡接口 ........................................................ 79

CAN接口 ............................................................... 80

IO扩展口 .............................................................. 81

开发板核心板原理图详解 ....................................................... 82

核心板电源 ............................................................. 82

ZYNQ主控芯片 ........................................................... 85

DDR3 SDRAM存储器 ....................................................... 88

6-Pin JTAG 接口 ......................................................... 91

PS复位按键 ............................................................. 92

PL LED ................................................................. 92

PS LED ................................................................. 93

PL时钟输入 ............................................................. 93

PS时钟输入 ............................................................. 93

PL配置状态指示灯 ...................................................... 94

PS端千兆以太网 ........................................................ 94

QSPI FLASH ............................................................ 96

eMMC .................................................................. 97

开发板使用注意事项 ........................................................... 98

ZYNQ的学习方法 ............................................................... 99

第二篇 软件篇 .................................................................. 101

Vivado软件的安装和使用 .................................................. 102

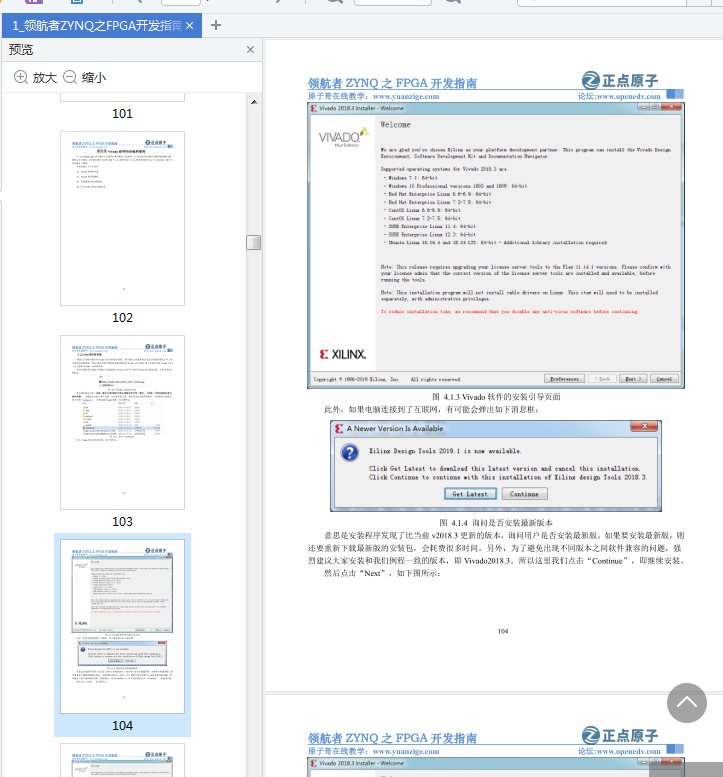

Vivado软件的安装 ............................................................ 103

Vivado软件的使用 ............................................................ 112

新建工程 .............................................................. 113

设计输入 .............................................................. 121

分析与综合 ............................................................ 127

约束输入 .............................................................. 131

设计实现 .............................................................. 134

下载比特流 ............................................................ 136

在线逻辑分析仪的使用 ........................................................ 141

HDL实例化调试探针流程.................................................. 142

Hardware Manager中观察调试信号 ......................................... 148

网表插入调试探针流程 .................................................. 153

在Vivado中进行功能仿真 ...................................................... 162

第三篇 语法篇 .................................................................. 178

Verilog HDL语法 ......................................................... 179

Verilog概述 ................................................................. 180

Verilog简介 ........................................................... 180

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

5

领航者ZYNQ之FPGA 开发指南

为什么需要Verilog ..................................................... 180

Verilog和VHDL区别 ..................................................... 180

Verilog和C的区别 ...................................................... 181

Verilog基础知识 ............................................................. 181

Verilog的逻辑值 ....................................................... 181

Verilog的标识符 ....................................................... 182

Verilog的数字进制格式.................................................. 182

Verilog的数据类型 ..................................................... 182

Verilog的运算符 ....................................................... 183

Verilog程序框架 ............................................................. 186

注释 .................................................................. 186

关键字 ................................................................ 186

程序框架 .............................................................. 187

Verilog高级知识点 ........................................................... 190

阻塞赋值(Blocking)................................................... 190

非阻塞赋值(Non-Blocking) ............................................. 191

assign和always区别 .................................................... 193

带时钟和不带时钟的always............................................... 193

什么是latch ........................................................... 194

状态机 ................................................................ 195

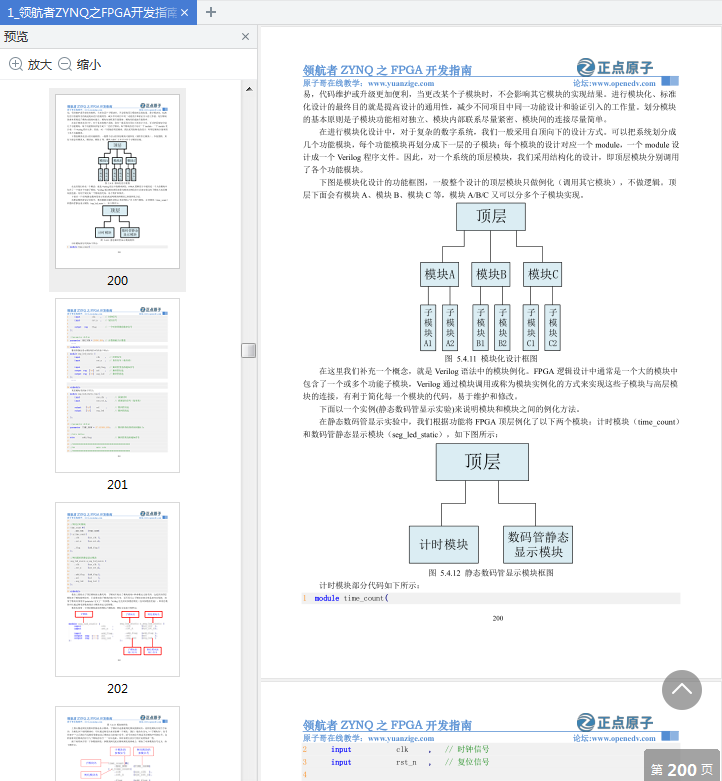

模块化设计 ............................................................ 199

Verilog编程规范 ............................................................. 203

编程规范重要性 ........................................................ 203

工程组织形式 .......................................................... 204

文件头声明 ............................................................ 204

输入输出定义 .......................................................... 205

parameter定义 ......................................................... 205

wirereg定义 .......................................................... 205

信号命名 .............................................................. 206

always块描述方式 ...................................................... 206

assign块描述方式 ...................................................... 207

空格和TAB ............................................................ 207

注释 ................................................................. 207

模块例化 ............................................................. 208

其他注意事项 ......................................................... 208

第四篇 实战篇 .................................................................. 210

LED灯闪烁实验 ........................................................... 211

LED灯简介 ................................................................... 212

实验任务 .................................................................... 212

硬件设计 .................................................................... 212

程序设计 .................................................................... 213

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

6

领航者ZYNQ之FPGA 开发指南

下载验证 .................................................................... 216

按键控制LED闪烁实验 ..................................................... 219

按键简介 .................................................................... 220

实验任务 .................................................................... 220

硬件设计 .................................................................... 220

程序设计 .................................................................... 221

下载验证 .................................................................... 223

按键控制蜂鸣器实验 ...................................................... 224

蜂鸣器简介 .................................................................. 225

实验任务 .................................................................... 225

硬件设计 .................................................................... 225

程序设计 .................................................................... 226

下载验证 .................................................................... 230

触摸按键控制LED灯实验 ................................................... 231

触摸按键简介 ................................................................ 232

实验任务 .................................................................... 232

硬件设计 .................................................................... 232

程序设计 .................................................................... 233

下载验证 .................................................................... 236

呼吸灯实验 .............................................................. 238

呼吸灯简介 ................................................................. 239

实验任务 ................................................................... 239

硬件设计 ................................................................... 239

程序设计 ................................................................... 240

下载验证 ................................................................... 242

IP核之MMCMPLL实验 ...................................................... 243

MMCMPLL IP核简介 .......................................................... 244

实验任务 ................................................................... 247

硬件设计 ................................................................... 247

程序设计 ................................................................... 248

下载验证 ................................................................... 255

IP核之RAM实验 ........................................................... 257

RAM IP核简介 ............................................................... 258

实验任务 ................................................................... 259

硬件设计 ................................................................... 259

程序设计 ................................................................... 259

下载验证 ................................................................... 267

IP核之FIFO实验 .......................................................... 269

FIFO IP核简介 .............................................................. 270

实验任务 ................................................................... 271

硬件设计 ................................................................... 271

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

7

领航者ZYNQ之FPGA 开发指南

程序设计 ................................................................... 271

下载验证 ................................................................... 284

UART串口通信实验 ........................................................ 286

UART串口简介 ............................................................... 287

实验任务 ................................................................... 288

硬件设计 ................................................................... 288

程序设计 ................................................................... 289

下载验证 ................................................................... 301

RS485串口通信实验 ....................................................... 304

RS-485简介 ................................................................. 305

实验任务 ................................................................... 305

硬件设计 ................................................................... 306

程序设计 ................................................................... 307

下载验证 ................................................................... 313

RGB TFT-LCD彩条显示实验.................................................. 315

RGB TFT-LCD简介 ............................................................ 316

实验任务 ................................................................... 322

硬件设计 ................................................................... 322

程序设计 ................................................................... 325

下载验证 ................................................................... 335

RGB TFT-LCD字符和图片显示实验 ............................................ 337

RGB TFT-LCD简介 ............................................................ 338

实验任务 ................................................................... 338

硬件设计 ................................................................... 338

程序设计 ................................................................... 338

下载验证 ................................................................... 350

HDMI彩条显示实验 ........................................................ 351

简介 ....................................................................... 352

实验任务 ................................................................... 355

硬件设计 ................................................................... 355

程序设计 ................................................................... 357

下载验证 ................................................................... 374

HDMI方块移动实验 ........................................................ 376

HDMI简介 ................................................................... 377

实验任务 ................................................................... 377

硬件设计 ................................................................... 377

程序设计 ................................................................... 377

下载验证 ................................................................... 381

EEPROM读写测试实验 ...................................................... 383

EEPROM简介 ................................................................. 384

实验任务 ................................................................... 389

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

8

领航者ZYNQ之FPGA 开发指南

硬件设计 ................................................................... 389

程序设计 ................................................................... 391

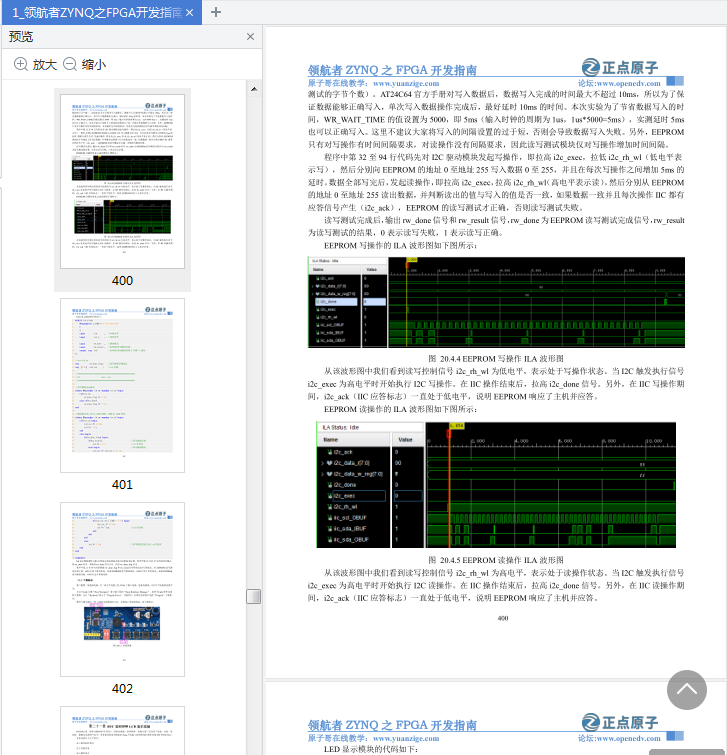

下载验证 ................................................................... 402

RTC实时时钟LCD显示实验............................................... 403

PCF8563简介 ................................................................ 404

实验任务 ................................................................... 406

硬件设计 ................................................................... 407

程序设计 ................................................................... 408

下载验证 ................................................................... 424

频率计实验 .......................................................... 425

等精度频率计简介 ........................................................... 426

实验任务 ................................................................... 427

硬件设计 ................................................................... 427

程序设计 ................................................................... 428

下载验证 ................................................................... 439

高速ADDA实验 ....................................................... 441

高速ADDA简介 .............................................................. 442

实验任务 ................................................................... 445

硬件设计 ................................................................... 445

程序设计 ................................................................... 448

下载验证 ................................................................... 456

MDIO接口读写测试实验................................................. 459

简介 ....................................................................... 460

实验任务 ................................................................... 466

硬件设计 ................................................................... 466

程序设计 ................................................................... 468

下载验证 ................................................................... 478

以太网ARP测试实验 ................................................... 481

简介 ....................................................................... 482

实验任务 ................................................................... 494

硬件设计 ................................................................... 494

程序设计 ................................................................... 496

下载验证 ................................................................... 518

以太网UDP测试实验 ................................................... 525

简介 ....................................................................... 526

实验任务 ................................................................... 530

硬件设计 ................................................................... 530

程序设计 ................................................................... 530

下载验证 ................................................................... 540

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

9

领航者ZYNQ之FPGA 开发指南

内容简介

领航者ZYNQ之FPGA开发指南将由浅入深的带领大家开启ZYNQ的学习之旅。本手册主要学习ZYNQ

的 PL(Program Logic,可编程逻辑)部分,共分为硬件篇、软件篇、语法篇与实战篇共四个篇章。

硬件篇:硬件篇主要介绍本手册的硬件实验平台以及硬件资源详解。

软件篇:软件篇主要介绍FPGA常用开发软件的安装教程与使用方法。

语法篇:语法篇主要介绍FPGA的硬件描述语言Verilog 的语法知识。

实战篇:实战篇主要通过21个实例带领大家一步步深入了解FPGA。

本手册为领航者ZYNQ 开发板的配套教程,在开发板配套的光盘里面,有开发板的原理图以及所有实

例的完整代码,这些代码都有详细的注释,所有源码都经过我们严格测试,不会有任何编译错误。另外,源代码有我们生成好的bit文件(用于下载程序的文件),大家只需要通过下载器下载到开发板即可看到实

验现象,亲自体验实验过程。

本手册不仅非常适合广大学生和电子爱好者学习FPGA,其大量的实验以及详细的注释,也是公司产品

开发的不二参考。

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

10

领航者ZYNQ之FPGA 开发指南

前 言

FPGA自诞生以来,经历了从配角到主角的过程,由于 FPGA飞速的发展,凭借其灵活性高、开发周期

短、并行计算效率高等优势,使其应用到越来越多的领域中,如通信、消费电子、工业控制以及嵌入式等

领域。

Zynq-7000系列是Xilinx 公司推出的全可编程片上系统(All Programmable SoC),包含PS(Processing

System,处理器系统)和PL (Programmable Logic,可编程逻辑)两部分。 Zynq SoC整合了 ARM双核cortex-A9

处理器和Xilinx 7 系列FPGA 架构,使得它不仅拥有ASIC在能耗、性能和兼容性方面的优势,而且具有

FPGA硬件可编程性的优点。

Zynq-7000系列具有丰富的型号,如XC7Z010、XC7Z020和XC7Z030等,领航者ZYNQ底板搭配的

核心板有两种型号,分别为ZYNQ-7020 (XC7Z020)和ZYNQ-7010 (XC7Z010)。 XC7Z020 内部的LC (Logic

Cell,逻辑单元)达到85K,XC7Z010的内部LC 为28K。对于我们学习使用以及项目开发来说,已经足够

了。

不管你是一个FPGA初学者,还是一个有经验的FPGA 工程师,本手册都非常适合。尤其对于初学者,本手册将手把手的教你如何使用 FPGA 的开发软件Vivado, 包括新建工程、编译、 下载调试等一系列步骤,让你轻松上手。

本手册的实验平台是领航者 ZYNQ 开发板,有这款开发板的朋友可以直接拿本手册配套的光盘上的例

程在开发板上运行、验证。而没有这款开发板而又想要的朋友,可以上淘宝购买。当然你如果有了一款自

己的开发板,而又不想再买,也是可以的,只要你的板子上有领航者ZYNQ开发板上的相同资源(需要实

验用到的),代码一般都是可以通用的,你需要做的就只是把引脚 IO的约束稍做修改,使之适合你的开发

板即可。

最后,手册在编写过程中难免会有出错的地方,如果大家发现手册中有什么错误的地方,还请告诉本

人一声,本人邮箱:3222632799@qq.com,也可以去www.openedv.com 论坛给我留言。在此先向各位朋友表

示真心的感谢。

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

11

领航者ZYNQ之FPGA 开发指南

第一篇 硬件篇

实践出真知,要想学好FPGA,实验平台必不可少!本篇我们将详细介绍用来学习 FPGA 的硬件平台:

领航者 ZYNQ 开发板。通过该篇的介绍,你将了解到我们的学习平台领航者 ZYNQ 开发板的功能及特点。

为了让读者更好的使用领航者ZYNQ开发板,本篇还介绍了开发板的一些使用注意事项,请读者在使

用开发板的时候一定要注意。

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

12

领航者ZYNQ之FPGA 开发指南

ZYNQ简介

ZYNQ是赛灵思公司(Xilinx)推出的新一代全可编程片上系统(APSoC),它将处理器的软件可编程

性与 FPGA 的硬件可编程性进行完美整合,以提供无与伦比的系统性能、灵活性与可扩展性。与传统SoC

解决方案不同的是,高度灵活的可编程逻辑(FPGA)可以实现系统的优化和差异化,允许添加定制外设与

加速器,从而适应各种广泛的应用。

本章包括以下几个部分:

1.1 ZYNQ简介

1.2 FPGA简介

1.3 ZYNQ PL简介

1.4 ZYNQ PS 简介

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

13

领航者ZYNQ之FPGA 开发指南

ZYNQ 简介

Zynq-7000系列是Xilinx 于2010年4月推出的行业第一个可扩展处理平台,旨在为视频监视、汽车驾

驶员辅助以及工厂自动化等高端嵌入式应用提供所需的处理能力与计算性能。 这款基于ARM处理器的SoC

可满足复杂嵌入式系统的高性能、低功耗和多核处理能力等要求。

ZYNQ的本质特征,是它组合了一个双核 ARM Cortex-A9处理器和一个传统的现场可编程门阵列

(FPGA)逻辑部件。由于该新型器件的可编程逻辑部分基于赛灵思 28nm工艺的7系列 FPGA,因此该系

列产品的名称中添加了“7000”,以保持与7 系列FPGA 的一致性,同时也方便日后本系列新产品的命名。

ZYNQ的全称是Zynq-7000 All Programmable SoC,也就是说, ZYNQ实际上是一个片上系统(System on

Chip,SoC)。那么,什么是“SoC”?

一个能够实现一定功能的电路系统由多个模块构成,如处理器、接口、存储器、模数转换器等等。这

些功能模块可以由分立的器件来实现,然后在印刷电路板(PCB)上组合起来,最终形成板上系统

(System-on-a-Board)。板上系统的示意图如下所示:

图 1.1.1 板上系统

在上图所示的板上系统中,绿色的矩形代表印刷电路板(PCB),上面各种颜色的小矩形代表了系统中

各个功能模块,如存储器等。这些模块的功能都由一个个独立的硅芯片分别实现的,它们之间通过 PCB 上

的金属走线连接,最终构成一个完整的系统。

而片上系统(System-on-Chip)指的是在单个硅芯片就可以实现整个系统的功能,其示意图如下所示:

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

14

领航者ZYNQ之FPGA 开发指南

图 1.1.2 片上系统

如上图所示,片上系统SoC 在一个芯片里就实现了存储、处理、逻辑和接口等各个功能模块,而不是

像板上系统那样,需要用几个不同的物理芯片来实现。与板上系统相比,SoC 的解决方案成本更低,能在

不同的系统单元之间实现更快更安全的数据传输,具有更高的整体系统速度、更低的功耗、更小的物理尺

寸和更好的可靠性。

在过去, SoC 这个术语常用于指专用集成电路(Application Specific Integrated Circuit, ASIC)。基于 ASIC

的 SoC 的代表性例子包括在PC、平板和智能手机上使用的处理器,如华为旗舰手机中的麒麟系列芯片。这

些处理器典型地是由至少两个处理器核、存储器、图形处理器、接口和其他功能模块组合起来的。基于ASIC

的 SoC 的主要缺点有两个:1、开发周期长且成本巨大;2、缺乏灵活性。开发ASIC时不可重用的工程投

入是巨大的,使得这种 SoC 类型只适合于大批量而且寿命有限的产品中。

ASIC SoC的局限性导致它们不适用于很多应用,特别是当快速投入市场能力、灵活性和升级能力已经

成为重要的关键因素。对于小批量或中批量的产品,ASIC SoC 也不是好的解决方案。

可编程片上系统(SOPC,System-on-Progammable-Chip)为上述应用提供了一个更灵活的解决方案:

一种在可编程、可重新配置的芯片上实现的 SoC。其中,可编程的芯片指的就是FPGA。FPGA天生的灵活

性使其可以被随心所欲地重新配置,以实现不同系统的功能,包括嵌入式处理器。和使用ASIC 来实现SoC

相比,FPGA 能构成更为基础灵活的平台,方便系统的升级。

相比于SOPC, ZYNQ为实现灵活的 SoC提供了一个更加理想的平台: Xilinx 将其打造成“全可编程 片

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

15

领航者ZYNQ之FPGA 开发指南

上系统(APSoC,All-Programmable SoC)”。它将处理器的软件可编程性与FPGA的硬件可编程性进行完

美整合,以提供无与伦比的系统性能、灵活性与可扩展性。

ZYNQ是由两个主要部分组成的:一个由双核ARM Cortex-A9为核心构成的处理系统(PS,Processing

System),和一个等价于一片 FPGA 的可编程逻辑(PL,Programmable Logic)部分。ZYNQ 架构的简化模

型如下图所示:

图 1.1.3 ZYNQ 架构简化模型

在上图中,PS具有固定的架构,包含了处理器和系统的存储器;而 PL 完全是灵活的,给了设计者一

块“空白画布”来创建定制的外设。

在ZYNQ 上,ARM Cortex-A9 是一个应用级的处理器,能运行像 Linux 这样的操作系统,而可编程

逻辑是基于 Xilinx 7系列的FPGA架构。ZYNQ 架构实现了工业标准的 AXI接口,在芯片的两个部分之间

实现了高带宽、低延迟的连接。这意味着处理器和逻辑部分各自都可以发挥最佳的用途,而不会产生在两

个分立器件之间的接口开销。与此同时,又能获得系统被简化为单一芯片所带来的好处,包括物理尺寸和

整体成本的降低。

FPGA 简介

通过前面的介绍,我们知道 ZYNQ 中集成了ARM处理器与 FPGA。ZYNQ作为一款全可编程SoC,其

中 FPGA的硬件可编程性功不可没。那么FPGA 是什么呢,它的灵活性又从何而来呢?

1) 数字集成电路的发展

在数字集成电路中,门电路是最基本的逻辑单元,用以实现最基本的逻辑运算(与、或、非)和复合

逻辑运算(与非、异或等)。与上述逻辑运算相对应,常用的门电路有与门、或门、非门、与非门、异或

门等,其电路符号如下图所示:

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

16

领航者ZYNQ之FPGA 开发指南

图 1.2.1 基本的门电路符号

在最初的数字逻辑电路中,每个门电路都是用若干个分立的半导体器件和电阻、电容连接而成的。不

难想象,用这种单元电路组成大规模的数字电路是非常困难的,这就严重制约了数字电路的普遍应用。1961

年,美国德州仪器公司(TI)率先将数字电路的元器件制作在同一片硅片上,制成了集成电路(Intergrated

Circuits,IC),并迅速取代了分立器件电路。

早期的数字逻辑设计需要设计师在一块电路板上或者如下图所示的面包板上用导线将多个芯片连接在

一起。每个芯片包含一个或多个逻辑门,或者一些简单的逻辑结构(比如触发器或多路复用器等)。如下

图中所示的芯片是在1960和 1970年代,很多设计中都会使用的德州仪器7400系列的器件。

图 1.2.2 使用74 系列器件搭建的电路

自20世纪60年代以来,随着集成电路工艺水平的不断进步,集成电路的集成度也不断提高。数字集

成电路经历了从小规模集成电路(Small Scale Integrated circuit,SSI),到中规模集成电路(Medium Scale

Integrated circuit,MSI),再到大规模集成电路(Large Scale Integrated circuit,LSI),然后是超大规模集

成电路(Very Large Scale Integrated circuit, VLSI), 以及甚大规模集成电路(Ultra Large Scale Integrated circuit,ULSI)的发展过程。今天我们已经可以把十分复杂的数字系统制作在一个很小的硅片上,构成 “片上系统”。

2) FPGA的由来

我们从逻辑功能的特点上将数字集成电路分类,可以分为通用型和专用型两类。前面介绍到的中、小

规模集成电路(如74系列) 都属于通用型数字集成电路。它们的逻辑功能都比较简单,而且是固定不变的。

由于它们的这些功能在组成复杂数字系统时经常要用到,所以这些器件具有很强的通用性。

从理论上来讲,用这些通用型的中、小规模集成电路可以组成任何复杂的数字系统。随着集成电路的

集成度越来越高,如果能把所设计的数字系统做成一片大规模集成电路,则不仅能减小电路的体积、重量

和功耗,而且可以使电路的可靠性大为提高。像这种为某种专门用途而设计的集成电路称为专用集成电路,即所谓的ASIC(Application Specific Integrated Circuit)。

ASIC 的使用在生产、生活中非常普遍,比如手机、平板电脑中的主控芯片都属于专用集成电路。

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

17

领航者ZYNQ之FPGA 开发指南

图 1.2.3 华为Mate 30手机中的麒麟 990芯片

虽然ASIC 有诸多优势,但是在用量不大的情况下,设计和制造这样的专用集成电路不仅成本很高,而

且设计制造的周期也很长。可编程逻辑器件(Programmable Logic Device,PLD)的出现成功解决了这个矛

盾。

可编程逻辑器件PLD 是作为一种通用器件生产,但它的逻辑功能是由用户通过对器件进行编程来设定

的。而且有些PLD 的集成度很高,足以满足设计一般数字系统的需要。这样就可以由设计人员自行编程从

而将一个数字系统“集成”在一片PLD 上,做成“片上系统”(System on Chip,SoC),而不必去请芯片

制造厂商设计和制作专用集成电路芯片了。

最后,我们再来总结一下这三种数字集成电路之间的差异。通用型数字集成电路和专用集成电路内部

的电路连接都是固定的,所以它们的逻辑功能也是固定不变的。而可编程逻辑器件则不同,它们内部单元

之间的连接是通过“写入”编程数据来确定的,写入不同的编程数据就可以得到不同的逻辑功能。

自20世纪70年代以来, PLD的研制和应用得到了迅速的发展,相继开发出了多种类型和型号的产品。

PLD 的发展历程如下图所示:

图 1.2.4 PLD 的发展历程

目前常见的PLD大体上可以分为 SPLD(simple PLD,简单PLD)、CPLD(complex PLD,复杂PLD)

和 FPGA(field-programmable gate array,现场可编程门阵列)。SPLD 中又可分为PLA、PAL和GAL几种

类型。FPGA 也是一种可编程逻辑器件,但由于在电路结构上与早期已经广为应用的 PLD 不同,所以采用

FPGA这个名称,以示区别。

通过对数字电路的学习我们知道,任何一个逻辑函数式都可以变换成与-或表达式,因而任何一个逻辑

函数都能用一级与逻辑电路和一级或逻辑电路来实现。PLD 最初的研制思想就来源于此。

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

18

领航者ZYNQ之FPGA 开发指南

图 1.2.5 PAL 器件的基本电路结构

上图是SPLD 中PAL(可编程阵列逻辑)的电路结构图。通过对输入端(inputs)到与门之间的可编程

阵列(programmable array)进行编程,利用 PAL 可以获得不同形式的组合逻辑函数。数字电路课程告诉我

们,任何逻辑函数式都可以转化为若干乘积项(product tems)之和的形式,亦称“积之和”形式。通过对

可编程阵列进行编程,与逻辑电路输出所需要的乘积项,再通过或逻辑电路将这些乘积项相加,就得到了

最终的功能输出。然后该输出送给输出电路中的寄存器用于存储或者同步,当然也可以忽略寄存器直接输

出。这就是PAL作为一种“可编程逻辑器件”能够实现不同逻辑功能的原理。

通过扩展SPLD的概念就可以得到CPLD。CPLD 是复杂可编程逻辑器件,相当于将多个PAL用可编程

互联阵列(Programmable Interconnect Array,PIA)连接起来,形成一个大的PLD,如下图所示:

图 1.2.6 CPLD结构示意图

上图中的Logic block(逻辑块)通常被称为逻辑阵列模块,或者LAB(Logic Array Block)。每个LAB

相当于一个PAL电路,不同型号的CPLD 器件可以包含十几个甚至上百个LAB。通过PIA将这些LAB连

接起来,就可以构成规模更大的逻辑电路了。另外,在 PAL 中,IO管脚是直接连接到逻辑的。而在CPLD

中,IO 管脚是通过PIA从器件的主要逻辑中分离出来的。IO管脚有它自己的控制逻辑,IO控制单元可以

根据需要将相应的引脚设置成输入、输出或双向工作模式。

CPLD相对于 SPLD最大的优势就是拥有更大的逻辑资源和布线的可能性。CPLD 中LAB 逻辑和 PIA

是完全可编程的,使得它具有在单芯片中非凡的设计灵活性。CPLD 的IO 特性和功能也远比 SPLD 中简单

的 IO更有价值。

FPGA 是在 PAL、GAL和CPLD等可编程逻辑器件的基础上进一步发展的产物,但是 FPGA和其前辈

CPLD 有着非常大的差异。

FPGA由许多 “可配置逻辑模块”(Configurable Logic Block, CLB)、 输入输出单元(IO Block,IOB)

和分布式的可编程互联矩阵(Programmable Interconnection Matrix,PIM)组成。在FPGA 中,CLB 被布置

成阵列的形式,如图 1.2.7所示。可编程的布线资源分布在 CLB 与CLB之间,像大城市的街道一样纵横联

接。这些布线资源分为行互联和列互联,可以跨过整个器件,也可以是局部CLB 之间的互联。

我们将图 1.2.6与图 1.2.7进行对比可以发现,FPGA 中的布线资源看上去似乎比CPLD 中的互联阵列

更简单,但它实际上提供了更大的功能性和连通性。FPGA中的布线资源使得器件中所有的逻辑资源都可以

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

19

领航者ZYNQ之FPGA 开发指南

与芯片内其他资源进行通信,这种结构可以实现更大容量、低成本的逻辑器件。

图 1.2.7 FPGA结构示意图

在前面所讲的各种SPLD和 CPLD电路中,都采用了与或逻辑阵列加上输出逻辑单元的结构形式。而

FPGA则采用了完全不同的电路结构形式(查找表,LUT),有关 FPGA 的结构我们将在本章ZYNQ PL简

介中作详细介绍。

3) FPGA的用途

在介绍FPGA 的用途之前,先给大家讲一个笑话:

话说一个资深工程师出国的时候带了一块 FPGA开发板。

海关问道:“这是什么东西?”

工程师说:“FPGA开发板”。

海关又问:“FPGA是什么?”。

工程师回答说:“你想让它是什么,它就是什么(It can be whatever you want)”

能看懂这个笑话就说明你已经对 FPGA 有了一定的了解。作为一种可编程器件,FPGA能实现任何数字

器件的功能,上至高性能CPU,下至简单的74电路,都可以用FPGA 来实现。FPGA 就像一张白纸,任由

你在上面涂鸦或者作画;FPGA又如同一堆积木,随便你用来搭建城堡或者玩“过家家”。

FPGA是什么这个问题可能不太好回答。但是如果说 FPGA用来干什么,那么答案就显而易见了。你可

能都还没意识到,在我们的生活中,FPGA 已经无处不在了。从你家里使用的高清电视,到附近的无线电接

收塔;从银行门口的ATM机,到微软数据中心的服务器,都可以看到FPGA的身影。

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

20

领航者ZYNQ之FPGA 开发指南

图 1.2.8 FPGA应用领域

如上图所示,FPGA广范应用在汽车、军用装备、图像处理、有线和无线通信、医药,以及工业控制等

诸多领域。

可编程逻辑天生就为并行地实现算法提供了理想的资源。比如在图像处理中,要同时对大量的像素点

进行数学运算,而FPGA就很适合像这种像素点级别的图像处理所需的快速、并行的操作。

FPGA并行的特性决定了它在某些特定行业应用上具有得天独厚的优势,例如在医疗领域。医学影像比

普通图像纹理更多,分辨率更高,相关性更大。因此,为严格确保临床应用的可靠性,对图像的压缩、分

割等预处理、图像分析及图像理解等要求更高。这些要求恰恰可以充分发挥FPGA的优势,通过FPGA 加

速图像压缩进程、删除冗余、提高压缩比、并确保图像诊断的可靠性。

在金融领域,由于采用流水线逻辑体系结构,数据流处理要求低延时,高可靠性。这在金融交易风险

建模算法应用中是重要的关键点,而 FPGA 正具备了这种优势。类似的行业和领域还有很多,特别是在深

度学习和神经网络,以及图像识别和自然语言处理等领域,FPGA正显示出其独有的优势。

ZYNQ PL 简介

ZYNQ PL部分等价于Xilinx 7 系列FPGA,因此我们将首先介绍 FPGA的架构。

简化的FPGA 基本结构由6部分组成,分别为可编程输入输出单元、基本可编程逻辑单元、嵌入式块

RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等,如下图所示:

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

21

领航者ZYNQ之FPGA 开发指南

图 1.3.1 FPGA基本结构

每个单元的基本概念介绍如下。

1) 可编程输入输出单元

输入输出(InputOuput)单元简称 IO 单元,它们是芯片与外界电路的接口部分,完成不同电气特性

下对输入输出信号的驱动与匹配需求,为了使FPGA 具有更灵活的应用,目前大多数 FPGA的 IO 单元被

设计为可编程模式,即通过软件的灵活配置,可以适配不同的电气标准与IO 物理特性;可以调整匹配阻抗

特性、上下拉电阻、以及调整驱动电流的大小等。

可编程IO单元支持的电气标准因工艺而异,不同芯片商、不同器件的 FPGA 支持的 IO标准不同,一

般来说,常见的电气标准有LVTTL,LVCMOS,SSTL,HSTL,LVDS,LVPECL和 PCI 等。值得一提的是,随着ASIC 工艺的飞速发展,目前可编程 IO支持的最高频率越来越高,一些高端FPGA 通过DDR寄存器

技术,甚至可以支持高达2Gbits 的数据数率。

ZYNQ上的通用输入输出功能(IOB)合起来被称作 SelectIO 资源,它们被组织成 50个IOB一组。每

个 IOB有一个焊盘,是与外部世界连接来做单个信号的输入或输出的。每个IOB 还包含一个 IOSERDES 资

源,可以做并行和串行数据的可编程转换。

可编程IO单元 可编程逻辑单元

嵌入式

块RAM

硬核

布线

资源

底层嵌入

功能单元

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

22

领航者ZYNQ之FPGA 开发指南

图 1.3.2 PL 中的 IOB

2) 基本可编程逻辑单元

基本可编程逻辑单元是可编程逻辑的主体,可以根据设计灵活地改变其内部连接与配置,完成不同的

逻辑功能。 FPGA一般是基于SRAM工艺的,其基本可编程逻辑单元几乎都是由查找表(LUT, Look Up Table)

和寄存器(Register)组成。Xilinx 7系列FPGA 内部查找表为 6输入,查找表一般完成纯组合逻辑功能。

FPGA内部寄存器结构相当灵活,可以配置为带同步异步复位或置位,时钟使能的触发器,也可以配置成

锁存器,FPGA依赖寄存器完成同步时序逻辑设计。

一般来说,比较经典的基本可编程逻辑单元的配置是一个寄存器加一个查找表,但是不同厂商的寄存

器与查找表也有一定的差异,而且寄存器与查找表的组合模式也不同。当然这些可编程逻辑单元的配置结

构随着器件的不断发展也在不断更新,最新的一些可编程逻辑器件常常根据需求设计新的LUT和寄存器的

配置比率,并优化其内部的连接构造。

例如,Altera可编程逻辑单元通常被称为LE(Logic Element),由一个寄存器加一个LUT构成。Altera

大多数 FPGA将 10个 LE有机地组合在一起,构成更大的功能单元――逻辑阵列模块(LAB,Logic Array

Block)。LAB中除了LE还包含 LE 之间的进位链,LAB控制信号,局部互联线资源,LUT级联链,寄存

器级联链等连线与控制资源。

Xilinx 7系列 FPGA中的可编程逻辑单元叫CLB(Configurable Logic Block,可配置逻辑块)每个CLB

里包含两个逻辑片(Slice)。每个 Slice由4 个查找表、8个触发器和其他一些逻辑所组成的。CLB示意图

如下所示:

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

23

领航者ZYNQ之FPGA 开发指南

图 1.3.3 CLB 示意图

CLB 是逻辑单元的最小组成部分,在PL中排列为一个二维阵列,通过可编程互联连接到其他类似的资

源。每个 CLB 里包含两个逻辑片,并且紧邻一个开关矩阵,如下图所示:

图 1.3.4 PL 中的CLB

3) 嵌入式块RAM

目前大多数FPGA 都有内嵌的块 RAM(Block RAM),FPGA内部嵌入可编程RAM模块,大大地拓

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

24

领航者ZYNQ之FPGA 开发指南

展了 FPGA 的应用范围和使用灵活性。不同器件商或不同器件族的内嵌块RAM的结构不同,Lattice常用的

块 RAM大小是9KBIT;Altera 的块RAM最灵活,一些高端器件内部同时含有3种块RAM结构,分别是

M512 RAM,M4K RAM,M9K RAM。

Zynq-7000里的块RAM和Xilinx 7 列FPGA 里的那些块 RAM是等同的,它们可以实现 RAM、 ROM 和

先入先出(First In First Out,FIFO)缓冲器。每个块 RAM 可以存储最多36KB 的信息,并且可以被配置

为一个36KB的RAM或两个独立的18KB RAM。默认的字宽是18位,这样的配置下每个RAM含有2048 个

存储单元。RAM 还可以被“重塑”来包含更多更小的单元(比如 4096个单元x9位,或 8192x4位),或

是另外做成更少更长的单元(如1024单元x36位512x72位)。把两个或多个块RAM组合起来可以形成更

大的存储容量。PL中的块RAM 示意图如下所示:

图 1.3.5 PL 中的Block RAM

需要补充的一点是,除了块 RAM,还可以灵活地将 LUT 配置成RAM,ROM,FIFO等存储结构,这

种技术被称为分布式 RAM。根据设计需求,块 RAM的数量和配置方式也是器件选型的一个重要标准。

4) 丰富的布线资源

布线资源连通FPGA内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速

度。FPGA芯片内部有着丰富的布线资源,这些布线资源根据工艺、长度、宽度和分布位置的不同而划分为

4 类不同的类别:

第一类是全局布线资源,用于芯片内部全局时钟和全局复位置位的布线;

第二类是长线资源,用以完成芯片Bank 间的高速信号和第二全局时钟信号的布线;

第三类是短线资源,用于完成基本逻辑单元之间的逻辑互连和布线;

第四类是分布式的布线资源,用于专有时钟、复位等控制信号线。

在实际中设计者不需要直接选择布线资源,布局布线器可自动地根据输入逻辑网表的拓扑结构和约束

条件选择布线资源来连通各个模块单元。从本质上讲,布线资源的使用方法和设计的结果有直接的关系。

5) 底层嵌入功能单元

底层嵌入功能单元的概念比较笼统,这里我们指的是那些通用程度较高的嵌入式功能模块,比如 PLL

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

25

领航者ZYNQ之FPGA 开发指南

(Phase Locked Loop)、DLL(Delay Locked Loop)、DSP、CPU等。随着FPGA 的发展,这些模块被越

来越多地嵌入到 FPGA 的内部,以满足不同场合的需求。

目前大多数FPGA 厂商都在 FPGA内部集成了DLL或者 PLL 硬件电路,用以完成时钟的高精度、低抖

动的倍频、分频、占空比调整、相移等功能。目前,高端 FPGA 产品集成的DLL和 PLL 资源越来越丰富,功能越来越复杂,精度越来越高。

另外,越来越多的高端FPGA 产品将包含DSP或 CPU 等硬核,从而FPGA 将由传统的硬件设计手段逐

步过渡到系统级设计平台。例如Altera的 Stratix IV、Stratix V 等器件内部集成了DSP 核;Xilinx的Virtes II

和 Virtex II pro系列FPGA内部集成了 Power PC450的处理器。FPGA 内部嵌入DSP或 CPU 等处理器,使

FPGA在一定程度上具备了实现软硬件联合系统的能力,FPGA 正逐步成为SOPC 的高效设计平台。

6) 内嵌专用硬核

这里的内嵌专用硬核与前面的底层嵌入单元是有区分的,这里讲的内嵌专用硬核主要指那些通用性相

对较弱,不是所有 FPGA器件都包含硬核。

在ZYNQ的PL端有一个数模混合模块――XADC,它就是一个硬核。 XADC包含两个模数转换器(ADC),一个模拟多路复用器,片上温度和片上电压传感器等。我们可以利用这个模块监测芯片温度和供电电压,也可以用来测量外部的模拟电压信号。

7) ZYNQ PL架构

在介绍完FPGA的基本结构之后,我们给出ZYNQ PL 架构的示意图,如下所示:

图 1.3.6 ZYNQ PL 架构示意图

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

26

领航者ZYNQ之FPGA 开发指南

ZYNQ PS简介

虽然我们在前面花费了大量的篇幅来介绍 ZYNQ 的PL 部分,但是 ZYNQ 实际上是一个以处理器为核

心的系统,PL只是它的一个外设。Zynq-7000系列的亮点在于它包含了完整的ARM处理器系统,且处理器

系统中集成了内存控制器和大量的外设,使Cortex-A9处理器可以完全独立于可编程逻辑单元。而且实际上

在 ZYNQ 中,PL 和PS两部分的供电电路是独立的,这样 PS或PL部分不被使用的话就可以被断电。

在前面我们介绍SOPC 时提到过,FPGA可以用来搭建嵌入式处理器,像Xilinx 的 MicroBlaze处理器

或者Altera的Nios II处理器。像这种使用FPGA 的可编程逻辑资源搭建的处理器我们称之为“软核”处理

器,它的优势在于处理器的数量以及实现方式的灵活性。

而ZYNQ 中集成的是一颗“硬核”处理器,它是硅芯片上专用且经过优化的硬件电路,硬核处理器的

优势是它可以获得相对较高的性能。另外,ZYNQ中的硬件处理器和软核处理器并不冲突,我们完全可以

使用 PL的逻辑资源搭建一个 Microblaze软核处理器,来和 ARM硬核处理器协同工作。

需要注意的是,Zynq 处理器系统里并非只有ARM处理器,还有一组相关的处理资源,形成了一个应

用处理器单元(Application Processing Unit,APU),另外还有扩展外设接口、cache 存储器、存储器接口、互联接口和时钟发生电路等。

ZYNQ 处理器系统(PS)示意图如下所示,其中红色高亮区域为APU。

图 1.4.1 PS 系统示意图

1) APU

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

27

领航者ZYNQ之FPGA 开发指南

图 1.4.2 APU 简化示意图

如上图所示是APU的简化框图。APU 主要是由两个ARM处理器核组成的,每个都关联了一些可计算

的单元:一个NEONTM媒体处理引擎(Media Processing Engine,MPE)和浮点单元(Floating Point Unit,FPU);一个内存管理单元(Memory Management Unit,MMU);和一个一级 cache 存储器(分为指令和

数据两个部分)。 APU 里还有一个二级 cache 存储器,再往下还有片上存储器 (On Chip Memory, OCM),这些是两个 ARM处理器共用的。最后,由一个一致性控制单元(Snoop Control Unit,SCU)在 ARM核和

二级 cache及OCM存储器之间形成了桥连接。SCU还部分负责与 PL对接,图中没有标出这个接口。

2) 外部接口

如图 1.4.1所示,Zynq PS 实现了众多接口,既有PS和PL之间的,也有 PS 和外部部件之间的。

PS 和外部接口之间的通信主要是通过复用的输入输出(Multiplexed InputOutput,MIO)实现的,它提供了可以灵活配置的 54 个引脚,这表明外部设备和引脚之间的映射是可以按需定义的。当需要扩

展超过 54个引脚的时候可以通过扩展 MIO(Extended MIO,EMIO)来实现,EMIO 并不是 PS 和外部连

接之间的直接通路,而是通过共用了 PL的IO 资源来实现的。

PS中可用的 IO包括标准通信接口和通用输入输出(General Purpose InputOutput,GPIO),GPIO 可以用做各种用途,包括简单的按钮、开关和 LED。如下图所示:

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

28

领航者ZYNQ之FPGA 开发指南

图 1.4.3 PS 的外部接口

3) 存储器接口

Zynq-7000 APSoC 上的存储器接口单元包括一个动态存储器控制器和几个静态存储器接口模块。动态存

储器控制器可以用于 DDR3、DDR3L、DDR2或LPDDR2。静态存储器控制器支持一个NAND闪存接口、一个Quad-SPI闪存接口、一个并行数据总线和并行 NOR 闪存接口。

4) 片上存储器

片上存储器包括256kB的RAM(OCM)和 128kB的ROM(BootROM)。OCM支持两个 64位AXI 从

机接口端口,一个端口专用于通过APU SCU的 CPUACP访问,而另一个是由PS和 PL内其他所有的总线

主机所共享的。BootROM是 ZYNQ 芯片上的一块非易失性存储器,它包含了ZYNQ所支持的配置器件的

驱动。BootROM对于用户是不可见的,专门保留且只用于引导的过程。

5) AXI接口

ZYNQ将高性能ARM Cotex-A系列处理器与高性能 FPGA在单芯片内紧密结合,为设计带来了如减小

体积和功耗、降低设计风险,增加设计灵活性等诸多优点。在将不同工艺特征的处理器与 FPGA融合在一

个芯片上之后,片内处理器与 FPGA 之间的互联通路就成了ZYNQ芯片设计的重中之重。如果Cotex-A9与

FPGA之间的数据交互成为瓶颈,那么处理器与FPGA 结合的性能优势就不能发挥出来。

Xilinx从Spartan-6和Virtex-6 系列开始使用AXI协议来连接 IP核。 在 7系列和 ZYNQ-7000 AP SoC器

件中,Xilinx在IP 核中继续使用 AXI协议。AXI的英文全称是 Advanced eXtensible Interface,即高级可扩

展接口,它是ARM公司所提出的AMBA(Advanced Microcontroller Bus Architecture)协议的一部分。

AXI协议是一种高性能、高带宽、低延迟的片内总线,具有如下特点:

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

29

领航者ZYNQ之FPGA 开发指南

1、总线的地址控制和数据通道是分离的;

2、支持不对齐的数据传输;

3、支持突发传输,突发传输过程中只需要首地址;

4、具有分离的读写数据通道;

5、支持显著传输访问和乱序访问;

6、更加容易进行时序收敛。

在数字电路中只能传输二进制数0和1,因此可能需要一组信号才能高效地传输信息,这一组信号就组

成了接口。AXI4协议支持以下三种类型的接口:

1、 AXI4:高性能存储映射接口。

2、 AXI4-Lite:简化版的AXI4 接口,用于较少数据量的存储映射通信。

3、 AXI4-Stream:用于高速数据流传输,非存储映射接口。

在这里首先我们首先解释一下存储映射(Meamory Map)这一概念。如果一个协议是存储映射的,那

么主机所发出的会话(无论读或写)就会标明一个地址。这个地址对应于系统存储空间中的一个地址,表

明是针对该存储空间的读写操作。

AXI4 协议支持突发传输,主要用于处理器访问存储器等需要指定地址的高速数据传输场景。AXI-Lite

为外设提供单个数据传输,主要用于访问一些低速外设中的寄存器。而AXI-Stream接口则像FIFO 一样,数据传输时不需要地址,在主从设备之间直接连续读写数据,主要用于如视频、高速AD、PCIe、DMA 接

口等需要高速数据传输的场合。

在PS和PL之间的主要连接是通过一组 9个AXI接口,每个接口有多个通道组成。这些形成了 PS 内

部的互联以及与 PL 的连接,如下图所示:

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

30

领航者ZYNQ之FPGA 开发指南

图 1.4.4 PS 与PL 的AXI互联

我们将上图中的接口总结如下所示:

图 1.4.5 PS 与PL的AXI接口

上图给出了每个接口的简述,标出了主机和从机(按照惯例,主机是控制总线并发起会话的,而从机

是做响应的)。需要注意的是,接口命名的第一个字母表示的是PS 的角色,也就是说,第一个字母 “M”

表示 PS 是主机,而第一个字母“S”表示 PS 是从机。

上图中PS和PL之间的9个AXI接口可以分成三种类型:

1、通用AXI(General Purpose AXI):一条 32 位数据总线,适合 PL 和PS之间的中低速通信。接口

是透传的不带缓冲。总共有四个通用接口:两个PS做主机,另两个 PL 做主机。

2、加速器一致性端口(Accelerator Coherency Port):在 PL 和 APU 内的 SCU 之间的单个异步连接,总线宽度为 64位。这个端口用来实现 APU cache 和PL 的单元之间的一致性。PL 是做主机的。

3、高性能端口(High Performance Ports):四个高性能 AXI 接口,带有FIFO缓冲来提供“批量”读

写操作,并支持PL和PS中的存储器单元的高速率通信。数据宽度是 32 或64 位,在所有四个接口中PL 都

是做主机的。

上面的每条总线都是由一组信号组成的,这些总线上的会话是根据 AXI4总线协议进行通信的。有关

AXI4 协议更详细的内容,我们将在后续的章节进行介绍。

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

31

领航者ZYNQ之FPGA 开发指南

实验平台简介

本章内容主要向大家简要介绍我们的实验平台:领航者ZYNQ开发板。通过本章的学习,你将对我们

后面使用的实验平台有个快速的了解,为后面的学习做铺垫。

本章包括以下几个部分:

2.1 领航者ZYNQ 开发板资源初探

2.2 领航者ZYNQ 开发板资源说明

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

32

领航者ZYNQ之FPGA 开发指南

领航者 ZYNQ 开发板资源初探

正点原子目前已经拥有多款 STM32、 I.MXRT以及FPGA开发板,这些开发板常年稳居淘宝销量冠军,累计出货超过 10W套。这款 ZYNQ 开发板,是正点原子针对中高端应用场景所推出的开发板,采用核心板

+底板的设计,方便用户对核心板进行二次开发。

领航者开发板底板资源

首先我们来看领航者ZYNQ 开发板的底板资源图,如图 2.1.1所示。

图 2.1.1 领航者ZYNQ 开发板底板资源图

从图 2.1.1可以看出,领航者ZYNQ开发板底板资源非常丰富,把ZYNQ 芯片内部的资源发挥到了极

致,同时扩充了丰富的接口和功能模块,整个开发板显得十分高端和大气。

开发板的外形尺寸为120mm160mm,板子的设计充分考虑了人性化设计,并结合正点原子多年的开发

板设计经验,经过多次改进,最终确定了这样的设计。

正点原子领航者开发板底板资源如下:

◆ 1个核心板接口,支持 ZYNQ7020ZYNQ-7010核心板

◆ EEPROM芯片:AT24C64,容量:64Kbit(8K 字节)

◆ 1个电源指示灯(蓝色)

◆ 2个PL LED(红色)

◆ 2个PS LED(红色)

◆ 1个有源蜂鸣器

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

33

领航者ZYNQ之FPGA 开发指南

◆ 1个PL 复位按键

◆ 2个PL 功能按键

◆ 2个PS 功能按键

◆ 1个电容触摸按键

◆ 1路CAN接口,CAN收发器采用TJA1050 芯片

◆ 1路RS232 串口(母)接口,采用SP3232 芯片

◆ 1路RS485 接口,和RS232 的接口复用

◆ 1个RS232RS485选择接口

◆ 1个CAN选择接口

◆ 1个标准的RGB888 TFT-LCD 接口

◆ 1个XADC接口

◆ 1个OLED摄像头模块接口

◆ 1个20x2扩展口,共36个扩展 IO口

◆ 1个RTC实时时钟,芯片型号为PCF8563

◆ 1个RTC电池座,并带电池

◆ 1个ATK MODULE 接口,支持正点原子蓝牙GPSUART等模块

◆ 1个BOOT 模式选择开关

◆ 1个电源指示灯

◆ 1路音频输出接口

◆ 1路音频输入接口

◆ 1个高性能音频编解码芯片 WM8960,支持录音、音频输入和音频输出

◆ 1个录音头(MIC麦克风)

◆ 1个小扬声器(位于开发板背面)

◆ 1路HDMI输入输出接口

◆ 4路USB HOST接口

◆ 1路USB SLAVE接口

◆ 14-Pin JTAG 接口,提供开发板下载和调试的功能

◆ 1组5V电源供应接入口

◆ 1组3.3V 电源供应接入口

◆ 3路3.3V 电源口和3路5V 电源口,方便给外扩模块供电

◆ 1个电源开关,控制整个开发板的电源

◆ 1个直流电源输入接口(输入电压范围:DC6~16V)

◆ 1个PL 端千兆以太网接口(RJ45)

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

34

领航者ZYNQ之FPGA 开发指南

◆ 1个PS 端千兆以太网接口(RJ45)

◆ 1个Micro SD(TF)卡接口(位于开发板背面)

◆ 1个USB 串口

领航者ZYNQ 开发板底板的特点包括:

1) 接口丰富。板子提供了丰富的标准外设接口,可以方便的进行各种外设的实验和开

发。

2) 设计灵活。我们采用核心板+底板的形式,板上很多资源都可以灵活配置,以满足不

同条件下的使用;板上很多资源都可以灵活配置,以满足不同条件下的使用。其中芯片左下

侧引出一排20x2扩展口,共36个扩展 IO 口。

3) 资源充足。板载高性能音频编解码芯片、HDMI接口、RGB LCD 接口、1个PL 千兆

网口+1个PS千兆网口、4个USB HOST接口+1个USB SLAVE 接口以及各种接口芯片,满

足各种应用需求。

4) 人性化设计,各个接口都有丝印标注,且用方框框出,使用起来一目了然;部分常

用外设大丝印标出,方便查找;接口位置设计合理,方便顺手。资源搭配合理,物尽其用。

领航者开发板核心板资源

接下来我们来看领航者ZYNQ 核心板资源图,正点原子的ZYNQ核心板根据主控芯片和DDR3 内存容

量的不同分为ZYNQ-7020核心板和ZYNQ-7010核心板。领航者ZYNQ-7020核心板和领航者ZYNQ-7010

核心板的资源图分别如图 2.1.2和图 2.1.3所示:

图 2.1.2 ZYNQ-7020 核心板资源图

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

35

领航者ZYNQ之FPGA 开发指南

图 2.1.3 ZYNQ-7010 核心板资源图

由图 2.1.2和图 2.1.3可知,ZYNQ核心板板载资源丰富,可以满足各种应用的需求。整个核心板的外

形尺寸为 45mm60mm,非常小巧,并且采用了贴片板对板连接器, 使得其可以很方便的应用在各种项目上。

ZYNQ-7020核心板和ZYNQ-7010核心板除ZYNQ 主控芯片和DDR3 存储容量不同外,其余外设完全

相同。ZYNQ-7020核心板和 ZYNQ-7010核心板具体资源如下:

◆ ZYNQ 芯片采用 Xilinx 公司的 ZYNQ7000 系列芯片,ZYNQ-7020 核心板的 ZYNQ

芯片型号为 XC7Z020CLG400-2,PL 逻辑单元多达 85K,BRAM 存储资源为 4.9Mbit;

ZYNQ-7010核心板的ZYNQ 芯片型号为XC7Z010CLG400-1,PL逻辑单元多达28K,BRAM

存储资源为2.1Mbit;两种ZYNQ芯片的处理器系统均为双核Cortex-A9结构。需要注意的是,ZYNQ-7020核心板主控芯片的速度等级为“-2”,ZYNQ-7010核心板主控芯片的速度等级为

“-1”,因此ZYNQ-7020核心板主控芯片的速度等级更高,所支持的频率也更高

◆ 2片DDR3 SDRAM,ZYNQ-7020核心板的DDR3型号为NT5CB256M16EP-DI,每

片4Gbit,总容量为 8Gbit (1GB); ZYNQ-7010核心板的 DDR3型号为NT5CB128M16IP-DI,每片2Gbit,总容量为4Gbit(512MB)

◆ 1个1x6下载接口,与底板的14-Pin JTAG接口功能一致

◆ 1个PL LED

◆ 1个PS LED

◆ 1个PL 晶振:50Mhz,给PL 可编程逻辑提供时钟

◆ 1个PS 晶振:33.333Mhzz,给 PS CPU 逻辑提供时钟

◆ 1个电源指示灯

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

36

领航者ZYNQ之FPGA 开发指南

◆ 1个PL 配置状态指示灯(DONE LED)

◆ 1个PS 端千兆以太网 PHY 芯片:RTL8211E-VL

◆ 1个PS 复位按键

◆ 1个QSPI FLASH,型号W25Q256FVEI,容量:256Mbit(32MB)

◆ 1个eMMC,型号为KLM8G1GETF,容量:8GB。

领航者ZYNQ 开发板底板的特点包括:

1) 体积小巧。核心板仅 45mm60mm 大小,方便使用到各种项目里面。

2) 集成方便。核心板使用两个240P BTB连接座,可以非常方便的集成到客户PCB上,更换简单,方便维修测试。

3) 资源丰富。核心板板载1GB512MB DDR3、32MB QSPI Flash、8GB eMMC 存储器,可以满足各种应用场合

4) 性能稳定。核心板采用 10层板设计,单独地层、电源层,保证运行稳定、可靠。

5) 人性化设计。核心板各种放有详细丝印,使用起来一目了然。资源搭配合理,物尽

其用。

6) 接口丰富。板子提供了丰富的标准外设接口,可以方便的进行各种外设的实验和开

发。

领航者 ZYNQ 开发板资源说明

领航者ZYNQ 开发板资源说明分为两个部分:硬件资源说明和软件资源说明。

硬件资源说明

领航者ZYNQ 开发板分别为 ZYNQ 的PL端和PS端配备了丰富的硬件外设,如下图所示:

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

37

领航者ZYNQ之FPGA 开发指南

图 2.2.1 领航者ZYNQ 开发板硬件资源框图

XC7Z020和XC7Z010 芯片的 PS端IO bank包括Bank 502、Bank 501和 Bank 500,PL端的 IO bank包

括 Bank 13、Bank 34和Bank 35,我们分别为PS 端和PL 端的IO 连接了不同的外设,如图 2.2.1所示。

下面我们分别介绍领航者ZYNQ核心板和底板上的硬件资源。

底板外设简介:

1. 有源蜂鸣器

领航者底板板载一个有源蜂鸣器(BEEP),可以实现简单的报警闹铃。

2. 1 个PL 复位按键

领航者底板板载一个PL 端的复位按键(PL_RESET),可以作为ZYNQ PL端逻辑的复位信号,按键

复位信号默认是高电平的,当复位按键按下之后为低电平。

3. 2 个PL LED

领航者底板板载2个PL LED灯(PL_LED0~PL_LED1),连接到了PL 端的 IO 口上。在调试代码的时

候,使用LED来指示程序执行状态,是非常不错的一个辅助调试方法。

4. 2 个PL 功能按键

领航者底板板载2个机械式按键(PL_KEY0~PL_KEY1)是直接连接在PL端的 IO口上的,可以作为

人机交互的输入信号。这2个按键信号默认都是高电平的,当按键被按下之后,按键信号变为低电平。

Bank 502

DDR 1.5V

DDR3 SDRAM

DDR3 SDRAM

Bank 501

MIO 1.8V

EMMC

千兆以太网

Bank 500

MIO 3.3V

QSPI FLASH

1个PS LED

Bank 13

Bank 34

Bank 35

3.3V

1个PL LED

Micro SD卡

USB 2.0 OTG

CH340 USB UART

2个PS LED

6PIN下载口 ZYNQ

14PIN JTAG

2个PL LED

PL复位按键

2个PL功能按键

PL触摸按键

有源蜂鸣器

UART串口

ATK Module

CAN接口

E2PROM

RTC实时时钟

音频编解码

XADC接口

RGB LCD接口

摄像头接口

千兆以太网接口

HDMI接口

40PIN扩展口

PS PL

ZYNQ芯片

ZYNQ核心板 领航者底板

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

38

领航者ZYNQ之FPGA 开发指南

5. 2 个PS LED

领航者底板板载2个PS LED灯(PS_LED0~PS_LED1),LED连接到了PS端的 IO 口上。

6. 2 个PS 功能按键

领航者底板板载2个机械式按键(PS_KEY0、PS_KEY1),按键都是直接连接在 PS 端的 IO 口上的,可以作为人机交互的输入信号。这 2个按键信号默认都是高电平的,当按键被按下之后,按键信号变为低

电平。

7. 1 个触摸按钮

领航者底板板载1个电容触摸输入按键(TPAD),触摸方案采用AR101芯片,该芯片利用电容充放电

原理,实现触摸按键检测的功能。当手指触摸TPAD 按键时,触摸芯片输出高电平,松开为低电平。

8. USB 转串口

领航者底板板载一个PS端的USB 转串口,之所以设计成USB 形式的串口,是出于现在电脑上串口正

在消失,尤其是笔记本,几乎清一色的没有串口。所以板载了USB 串口可以方便大家进行 USB串口通信的

试验。同时这个USB接口还可以给开发板提供电源, 但是其最大电流只有500mA, 但是在运行PS端的ARM

处理器时它却不能够提供足够大的电流,所以还是建议大家使用专门的电源适配器来为开发板供电。

9. RS232 接口(母头)

领航者底板板载一个普通RS232 接口,通过一个标准的 DB9 母头和外部的串口连接。通过这个接口,领航者可以连接带有串口的电脑或者其他设备,实现串口通信的功能。

10. RS485接口

领航者底板板载一个RS485 接口,通过一个两PIN的端子和外部的485接口连接。通过这个接口,领

航者可以连接带有RS485接口的开发板或者其他设备,实现 RS485通信的功能。 这里提醒大家, 两个RS485

接口进行通信的时候,必须A 接A,B接B,否则可能通信不正常!

11. RGB TFT-LCD接口

领航者底板板载一个RGB LCD接口,可以连接各种分辨率的正点原子RGB LCD 屏,采用的是RGB888

格式,可显示1677万色,色彩显示丰富。并且支持触摸的功能。

12. XADC接口

领航者底板板载一个XADC 接口(J1),用于测量外部输入的模拟电压,范围为 0~1V。ZYNQ内部的

XADC模块既可以测量ZYNQ 芯片内部的温度和电压,也可以用来测量外部的模拟电压。

13. OLED摄像头模块接口

领航者底板板载一个OLED摄像头模块接口(P2)。如果是正点原子的摄像头模块,则刚好可以直接

插上去。通过这个接口,可以分别完成OLED 显示或者摄像头显示实验。

14. EEPROM (AT24C64)

领航者底板板载一个I2C接口的EEPROM芯片,容量为 64Kbit,也就是8K字节。用于存储一些掉电

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

39

领航者ZYNQ之FPGA 开发指南

不能丢失的重要数据,比如系统设置的一些参数等。有了这个就可以方便的实现掉电数据保存。

15. RTC实时时钟

领航者底板板载一个RTC实时时钟芯片(U6),芯片型号为PCF8563。PCF8563 是PHILIPS 公司推出

的一款工业级多功能时钟日历芯片,具有报警功能、定时器功能、时钟输出功能以及中断输出功能,能完

成各种复杂的定时服务。

16. 电池接口

领航者底板板载一个RTC实时时钟的供电接口(BAT1),可以保证在开发板断电时,实时时钟仍然能

够继续工作,这样的话,配置的日期与时间不会因开发板的断电而恢复到默认值。

17. ATK MODULE接口

领航者底板板载一个ALIENTEK 通用模块接口(U4),目前可以支持 ALIENTEK 开发的 GPS 模块、蓝牙模块、MPU6050 模块和全彩 RGB 灯模块等,直接插上对应的模块,就可以进行相关模块的开发。后

续我们将开发更多兼容该接口的其他模块,实现更强大的扩展性能。

18. BOOT模式选择开关

领航者底板板载一个ZYNQ的 BOOT模式选择开关(BOOT_CFG),用于设置 PS端在上电后的启动

源,包括 JTAG、NAND、QSPI FLASH和SD Card。

19. 电源指示灯

领航者底板板载1颗蓝色的 LED 灯(PWR),用于指示电源状态。在电源开启的时候电源指示灯会处

于点亮的状态,否则为熄灭的状态。通过这个LED,可以判断开发板的上电情况。

20. 耳机输出接口

领航者底板板载1个音频输出接口(PHONE),该接口可以插入 3.5mm的耳机。当 WM8960播放音

乐的时候,就可以通过在该接口插入耳机来欣赏音乐。

21. 音频输入接口

领航者底板板载1个音频输入接口(LINE_IN),该接口可以通过音频线来连接电脑或者手机的耳机接

口。

22. MIC(麦克风)

领航者底板板载1个录音输入口(MIC,即麦克风),该麦克风直接连接到WM8960的录音输入通道

上,可以实现录音的功能。

23. 扬声器

这是开发板自带的一个小喇叭(SPEAKER),安装在开发板的背面,可以用来播这放音乐。该喇叭由

WM8960直接驱动。

24. HDMI接口

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

40

领航者ZYNQ之FPGA 开发指南

领航者底板板载1个HDMI(High Definition Multimedia Interface,HDMI)接口,该接口可以连接到

HDMI显示器上,从而显示出视频或者图片等。开发板没有板载HDMI的PHY 芯片,HDMI的PHY 编解

码功能由ZYNQ PL逻辑来模拟实现。

25. 14-Pin JTAG接口

领航者底板板载1个14针标准 JTAG调试口(JTAG),该 JTAG 口与核心板的6-Pin JTAG接口在硬件

上是连在一起的,可以直接和 FPGA 下载器(调试器)连接,用于下载程序或者对程序进行在线调试。

26. 3.3V 电源输入输出

领航者底板板载1组3.3V电源输入输出排针(23),用于给外部提供 3.3V的电源,也可以从外部接

3.3V 的电源给板子供电。大家在做实验的时候可能经常会为没有3.3V 电源而苦恼不已,有了领航者 ZYNQ

开发板,你就可以很方便的拥有一个简单的 3.3V 电源(最大电流不能超过 500mA)。

27. 5V电源输入输出

领航者底板板载1组5V电源输入输出排针(23),该排针用于给外部提供5V 的电源,也可以从外

部接 5V的电源给板子供电。同样大家在实验的时候可能经常会为没有5V电源而苦恼不已,正点原子充分

考虑到了大家的需求,有了这组 5V 排针,你就可以很方便的拥有一个简单的 5V 电源(USB 供电的时候,最大电流不能超过 500mA,外部供电的时候,最大可达 1000mA)。

28. 电源开关

领航者底板板载1个电源开关(K1)。该开关用于控制整个开发板的供电,如果通过开关切断电源,则整个开发板都将断电,电源指示灯(PWR)会随着此开关的状态而亮灭。

29. DC6~16V电源输入

领航者底板板载1个外部电源输入口(DC_IN),采用标准的直流电源插座。开发板板载了DC-DC 芯

片(JW5060T),用于给开发板提供高效、稳定的5V电源。由于采用了DC-DC 芯片,所以开发板的供电

范围十分宽,大家可以很方便的找到合适的电源(只要输出范围在 DC6~16V 的基本都可以)来给开发板供

电。在耗电比较大的情况下,比如用到 4.3寸屏7寸屏网口高速AD-DA 的时候,建议大家使用外部电源

供电,可以提供足够的电流给开发板使用。

30. PL端千兆以太网接口(RJ45)

领航者底板板载1个千兆的RJ45网口(PL_GE), 连接到了 PL端的IO 口上, PHY芯片型号是B50610,支持 10Mbps100Mbps1000Mbps的通信速率,板载的RJ45 插座可以连接网线,实现网络通信功能。

31. PS端千兆以太网接口(RJ45)

领航者底板板载1个千兆的 RJ45 网口(PS_GE),通过转接板连接到了核心板上的以太网 PHY芯片,支持 10Mbps100Mbps1000Mbps的通信速率,板载的RJ45 插座可以连接网线,实现网络通信功能。

32. USB2.0 接口

领航者开发板为PS端的USB模块配备了一个USB2.0 PHY芯片,并且根据主从模式的不同,外接了 4

个HOST模式的接口和一个SLAVE模式的接口。 4个HOST模式的接口可分别用来连接不同的USB SLAVE

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

41

领航者ZYNQ之FPGA 开发指南

设备,可以用来连接鼠标、键盘等不同的设备,以满足各种不同的需求。一个 SLAVE模式的接口可以用来

连接HOST 设备,以满足特定的应用需求。

33. Micro SD 接口

领航者底板板载1个标准Micro SD 接口(TF_CARD),该接口位于开发板的背面,采用 Micro SD接

口,可以使用 SPISDIO驱动方式。有了这个接口,就可以满足海量数据存储的需求。

34. CAN 接口

领航者底板板载一个CAN总线通信接口,CAN 接口通过 2个端口和外部CAN总线连接,即CANH

和 CANL。这里提醒大家:两个 CAN 接口通信的时候,CANH必须接CANH,CANL必须接CANL,否则

可能通信不正常!

35. 40PIN 扩展口

领航者底板板载一个40PIN 的扩展口, 位于开发板的左下角,扩展口规格是220 Pin,采用标准2.54MM

排针间距,其中包括 36个IO口,1个+3.3V,1个+5V,2 个GND。它可以用来连接不同的功能模块,例

如,正点原子开发的高速ADDA模块和双目摄像头模块等。

核心板外设简介:

1. ZYNQ主控芯片

ZYNQ-7020核心板主控芯片为XC7Z020CLG400-2,85K LC(逻辑单元),4.9Mbit BRAM;

ZYNQ-7010核心板主控芯片为XC7Z010CLG400-1,28K LC(逻辑单元),2.1Mbit BRAM。

Zynq处理器系统里包含两个 Cortex-A9处理器,除此之外,还有一组相关的处理资源,形成了一个应

用处理器单元(Application Processing Unit,APU)。另外处理器系统里还有扩展外设接口、cache存储器、存储器接口、互联接口和时钟发生电路等。

2. DDR3 SDRAM

ZYNQ-7020核心板板载两片4Gbit DDR3内存,芯片型号为NT5CB256M16EP-DI,总容量为8Gbit (1GB);

ZYNQ-7010核心板板载两片2Gbit DDR3内存,芯片型号为NT5CB128M16IP-DI,总容量为4Gbit (512MB);

板载的DDR3芯片可以轻松应对各种大内存、高带宽场景需求,比如摄像头图像数据存储等。此外,DDR3 内存也作为PS 端处理器的运行内存。

3. 1 个6-Pin下载接口

核心板的6-PIN下载接口与底板的 14-Pin JTAG接口是一体的,可以在单独使用核心板时做调试和下载

使用。

4. 1 个PL LED

它连接到了PL 端的用户 IO 上,可由用户编写Verilog 代码来控制其亮灭。

5. 1 个PS LED

它连接到了PS端的GPIO上,可由用户使用C 代码编程来控制其亮灭。

6. PL端 50Mhz晶振

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

42

领航者ZYNQ之FPGA 开发指南

这是开发板上用于为ZYNQ PL 端提供时钟的晶振(XTAL)。该晶振输出的时钟是PL端最原始的时

钟,其它外设需要的各种频率的时钟都在此基础上进行倍频或分频。

7. PS 端33.333Mhz晶振

这是开发板上用于为ZYNQ PL 端提供时钟的晶振(XTAL) 。 该晶振输出的时钟是 PS端最原始的时钟,PS 端外设所需要的各种频率的时钟都在此基础上进行倍频或分频。

8. 电源指示灯(PW)

这是核心板板载的一颗蓝色的LED灯(PWR),用于指示电源状态。在电源开启的时候电源指示灯会

处于点亮的状态,否则为熄灭的状态。通过这个 LED,可以判断开发板的上电情况。需要说明的是,ZYNQ

核心板没有独立的供电接口,需要通过BTB转接板连接底板,由底板上的转接板进行供电。

9. PL 配置状态指示灯(DONE LED)

这是核心板板载的一颗PL配置状态指示灯,连接到了 PL 端的配置完成(DONE)信号,在PL端配置

(下载程序)完成之后,该 LED 灯会被点亮。

10. PS千兆以太网 PHY 芯片

这是核心板板载的一颗PS端千兆以太网PHY (物理)芯片,型号为 RTL8211E-VL,实现了 101001000M

以太网物理层功能。该 PHY 芯片的引脚连接到了底板上的 RJ45 接口上,能够满足高带宽通信的需求。

11. PS端复位按键(PS_RST)

ZYNQ PS 端的复位按键,它连接到了 PS端的复位逻辑,按下后,PS 端将重新从上电后的状态开始运

行。

12. QSPI Flash(W25Q256FVEI)

这是开发板的Flash芯片,存储容量为256Mbit(32M字节),用于存储ZYNQ 芯片的镜像数据,包括

PS 端的程序数据和PL端的配置镜像。

13. eMMC

eMMC是非易失性NAND存储器,俗称电子硬盘,领航者核心板的eMMC芯片型号为KLM8G1GETF,存储容量为 8GB,能够满足PS端的大容量非易失性存储需求。

软件资源说明

上面我们简单介绍了领航者 ZYNQ 开发板的硬件资源。接下来,我们将向大家简要介绍一下领航者

ZYNQ开发板的软件资源。

领航者ZYNQ 开发板PL端提供的标准例程多达21个,领航者 ZYNQ 开发板PS 端提供的标准例程多

达 35个。我们提供的这些例程,全部都是原创自主开发,注释非常详细、代码风格统一、难易程度由浅入

深,非常适合初学者入门。而其他家开发板的例程,要么注释比较少,要么工程文件管理不统一,对初学

者来说可能很难入门。

领航者ZYNQ 开发板PL端的例程列表如下表所示:

表 2.2.1 领航者ZYNQ 开发板 PL端的例程

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

43

领航者ZYNQ之FPGA 开发指南

编号 实验名称 编号 实验名称

1 LED闪烁实验 12 RGB LCD字符和图片显示实验

2 按键控制LED灯实验 13 HDMI彩条显示实验

3 按键控制蜂鸣器实验 14 HDMI方块移动实验

4 触摸按键控制LED灯实验 15 EEPROM读写实验

5 呼吸灯实验 16 RTC实时时钟LCD显示实验

6 IP核之MMCMPLL实验 17 频率计实验

7 IP核之RAM实验 18 高速ADDA实验

8 IP核之FIFO实验 19 MDIO接口读写测试实验

9 UART串口通信实验 20 以太网ARP实验

10 RS485串口通信实验 21 以太网UDP测试实验

11 RGB TFT-LCD彩条显示实验

领航者 ZYNQ 开发板PS端的例程列表如下表所示:

表 2.2.2 领航者 ZYNQ 开发板 PS 端的例程

编号 实验名称 编号 实验名称

1 Hello World实验 19 SD卡读BMP图片LCD显示实验

2 MIO控制LED闪烁实验 20 SD卡读BMP图片HDMI显示实验

3 EMIO按键控制LED实验 21 OV7725摄像头LCD显示实验

4 MIO按键中断控制LED实验 22 OV7725摄像头HDMI显示实验

5 AXI GPIO按键控制LED实验 23 OV5640摄像头LCD显示实验

6 自定义IP核-控制呼吸灯实验 24 OV5640摄像头HDMI显示实验

7 固化程序(PS、PS+PL)实验 25 OV7725摄像头Sobel边沿检测实验

8 UART串口中断实验 26 OV7725照相机实验

9 定时器中断实验 27 RGB LCD触摸画板实验

10 PS XADC接口实验 28 双目OV5640摄像头LCD显示实验

11 QSPI Flash读写测试实验 29 双目OV5640摄像头HDMI显示实验

12 SD卡读写TXT文本实验 30 基于lwip的echo server实验

13 双核AMP实验 31 基于lwip的TCP服务器性能测试实验

14 基于BRAM的PL和PS的数据交互 32 基于lwip的tftp server实验

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

44

领航者ZYNQ之FPGA 开发指南

15 AXI4接口之DDR读写实验 33 基于TCP的远程更新QSPI实验

16 AXI DMA环路测试 34 基于UDP的远程更新QSPI实验

17 IP核封装与接口定义 35 音频环回实验

18 PS通过VDMA驱动LCD显示实验

从上表可以看出,领航者ZYNQ开发板的例程是非常丰富的,并且扩展了很多有价值的例程。各个例

程的难度是循序渐进的,首先从最基础的 LED 灯闪烁实验开始,然后一步步深入,从简单到复杂,有利于

大家的学习和掌握,所以,领航者ZYNQ开发板是非常适合初学者的。当然,对于想深入学习ZYNQ开发

的朋友,领航者ZYNQ 开发板也是一个绝佳的选择。

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

45

领航者ZYNQ之FPGA 开发指南

硬件资源详解

本章,我们将向大家详细介绍领航者ZYNQ 开发板各部分的硬件原理图,让大家对领航者ZYNQ开发

板的各部分硬件原理有个深入理解,并向大家介绍开发板的使用注意事项,为后面的学习做好准备。

本章包括以下几个部分:

3.1 领航者ZYNQ 的IO分配

3.2 核心板外设详解

3.3 底板外设详解

3.4 开发板使用注意事项

3.5 ZYNQ的学习方法

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

46

领航者ZYNQ之FPGA 开发指南

领航者 ZYNQ 的IO分配

ZYNQ-7020核心板的主控芯片为XC7Z020CLG400-2,ZYNQ-7010核心板的主控芯片为

XC7Z010CLG400-1。XC7Z020芯片比XC7Z010芯片多出一个 BANK,即 BANK13。为了使ZYNQ-7020

核心板和ZYNQ-7010核心板的引脚完全兼容,ZYNQ-7020 核心板的BANK 13我们没有连接到任何硬件外

设,即没有引出至BTB 转接板。

XC7Z020芯片有6个用户IO BANK(比XC7Z010多一个 BANK)和最大253个用户 IO,了解器件

的 IO分配方式,有助于我们在硬件设计时根据器件的一些约束,对设计进行合理的 IO分配,减少硬件出

错的可能性。ZYNQ的IO口分成了PL和PS 两部分,我们将分别介绍 PL和 PS 两部分的 IO分配。

PL端的IO分配

ZYNQ的PL 侧和传统FPGA 一样,可以灵活地分配到不同的IO 口上。在XC7Z020中,PL端的IO被

分成了 3组,每一组称为一个 IO Bank,分别是BANK13、BANK34、BANK35。同一个Bank 中的所有IO

供电相同,而各个Bank的IO供电可以不同,领航者开发板都将它们连接到了3.3V的电源上。PL 端的 3

个 IO BANK 分别如图 3.1.1、图 3.1.2和图 3.1.3所示:

图 3.1.1 PL 端的BANK13

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

47

领航者ZYNQ之FPGA 开发指南

图 3.1.2 PL 端的BANK34

图 3.1.3 PL 端的BANK35

需要说明的是, XC7Z020芯片比XC7Z010芯片多出一个BANK13, 为了使这两颗芯片的引脚完全兼容,XC7Z020芯片的BANK13没有连接到任何硬件外设。

为了让大家更快更好的使用我们的领航者ZYNQ 开发板,这里特地将ZYNQ PL 端的 IO 引脚分配做了

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

48

领航者ZYNQ之FPGA 开发指南

一个总表,以便大家查阅。领航者ZYNQ PL端 IO引脚分配总表如下表所示:

表 3.1.1 领航者ZYNQ PL端 IO引脚分配总表

信号名 方向 管脚 端口说明

系统时钟(50Mhz)

sys_clk input U18 系统时钟,频率:50Mhz

PL复位按键

sys_rst_n input J15 PL复位复位,低电平有效

2个PL功能按键

key[0] input L20 PL按键KEY0

key[1] input J20 PL按键KEY1

3个PL_LED灯

led[0] output J18 (底板)PL_LED0

led[1] output H18 (底板)PL_LED1

led output J16 (核心板)PL_LED

触摸按键

touch_key input L19 触摸按键

蜂鸣器

beep output G18 蜂鸣器

RS232RS485串口

uart_rxd input J14 串口接收端

uart_txd output K18 串口发送端

ATK MODULE

uart_rx input P19 RXD端口

uart_tx output N18 TXD端口

gbc_key input J20 KEY端口

gbc_led output H20 LED端口

IIC总线(EEPROMRTC实时时钟

音频配置)

iic_scl output M17 IIC时钟信号线

iic_sda inout M18 IIC双向数据线

CAN总线

can_rx input R19 CAN总线接收

can_tx output T19 CAN总线发送

RGB TFT-LCD接口

lcd_hs output U17 RGB LCD行同步

lcd_vs output P20 RGB LCD场同步

lcd_de output N20 RGB LCD数据使能

lcd_bl output Y16 RGB LCD背光控制

lcd_clk output T16 RGB LCD像素时钟

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

49

领航者ZYNQ之FPGA 开发指南

lcd_rgb[0] output Y18 RGB LCD蓝色(最低位)

lcd_rgb[1] output Y19 RGB LCD蓝色

lcd_rgb[2] output W20 RGB LCD蓝色

lcd_rgb[3] output V20 RGB LCD蓝色

lcd_rgb[4] output U14 RGB LCD蓝色

lcd_rgb[5] output U15 RGB LCD蓝色

lcd_rgb[6] output T20 RGB LCD蓝色

lcd_rgb[7] output U20 RGB LCD蓝色(最高位)

lcd_rgb[8] output W14 RGB LCD绿色(最低位)

lcd_rgb[9] output Y14 RGB LCD绿色

lcd_rgb[10] output N15 RGB LCD绿色

lcd_rgb[11] output N16 RGB LCD绿色

lcd_rgb[12] output V16 RGB LCD绿色

lcd_rgb[13] output W16 RGB LCD绿色

lcd_rgb[14] output W18 RGB LCD绿色

lcd_rgb[15] output W19 RGB LCD绿色(最高位)

lcd_rgb[16] output T10 RGB LCD红色(最低位)

lcd_rgb[17] output T11 RGB LCD红色

lcd_rgb[18] output P14 RGB LCD红色

lcd_rgb[19] output R14 RGB LCD红色

lcd_rgb[20] output V13 RGB LCD红色

lcd_rgb[21] output U13 RGB LCD红色

lcd_rgb[22] output G15 RGB LCD红色

lcd_rgb[23] output H15 RGB LCD红色(最高位)

lcd_scl output V17 触摸屏IIC接口的时钟

lcd_sda inout M19 触摸屏IIC接口的数据

ct_rst output Y17 触摸屏的复位

ct_int input V18 触摸屏的中断

HDMI接口

tmds_data_p[0] output K19 HDMI的DATA0通道的 P端

tmds_data_p[1] output M14 HDMI的DATA1通道的 P端

tmds_data_p[2] output L16 HDMI的DATA2通道的 P端

tmds_clk_p output L14 HDMI的CLK通道的 P端

tmds_oen output G17 HDMI的输出使能信号

tmds_scl output V17 HDMI的SCL信号

tmds_sda output M19 HDMI的SDA信号

tmds_cec output H16 HDMI的消费类电子控制信号

tmds_hpd input H17 HDMI的热插拔信号

摄像头接口(OV5640OV7725)

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

50

领航者ZYNQ之FPGA 开发指南

cam_sgm_ctrlcam_pwdn output R17

OV7725时钟选择信号(0:使用引

脚XCLK提供的时钟 1:使用摄像

头自带的晶振提供时钟)

OV5640电源休眠控制信号

cam_rst_n output P15 cmos 复位信号,低电平有效

cam_vsync input R18 cmos 场同步信号

cam_href input T17 cmos 行同步信号

cam_pclk input T15 cmos 数据像素时钟

cam_data[0] input P16 cmos 数据

cam_data[1] input V15 cmos 数据

cam_data[2] input W15 cmos 数据

cam_data[3] input T12 cmos 数据

cam_data[4] input U12 cmos 数据

cam_data[5] input V12 cmos 数据

cam_data[6] input W13 cmos 数据

cam_data[7] input T14 cmos 数据

cam_scl output P18 cmos SCCB时钟信号线

cam_sda inout N17 cmos SCCB双向数据线

音频(WM8960)

aud_bclk input B19 WM8960的位时钟

aud_daclrc input B20 WM8960的对齐时钟

aud_adclrc input C20 WM8960的对齐时钟

aud_adcdat input A20 WM8960的ADC数据线

aud_dacdat output K16 WM8960的DAC数据线

aud_mclk output U19 WM8960的主时钟

PL端以太网RGMII接口

eth_rst_n output G14

以太网芯片复位信号,低电平有

效

eth_rx_clk input K17 RGMII接收数据时钟

eth_rx_ctl input D19 RGMII输入数据有效信号

eth_rxd[0] input F19 RGMII输入数据RXD[0]

eth_rxd[1] input F20 RGMII输入数据RXD[1]

eth_rxd[2] input E17 RGMII输入数据RXD[2]

eth_rxd[3] input D18 RGMII输入数据RXD[3]

eth_tx_clk input G19 RGMII发送数据时钟

eth_tx_ctl output E19 RGMII输出数据有效信号

eth_tx_data[0] output G20 RGMII输出数据TXD[0]

eth_tx_data[1] output F16 RGMII输出数据TXD[1]

eth_tx_data[2] output F17 RGMII输出数据TXD[2]

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

51

领航者ZYNQ之FPGA 开发指南

eth_tx_data[3] output E18 RGMII输出数据TXD[3]

eth_mdc output K14 以太网管理接口的时钟

eth_mdio inout D20 以太网管理接口的双向数据

在上表中,表格中列出来了除扩展口外,开发板上所有的 PL IO 引脚,扩展口上的引脚 IO可以参考开

发板的原理图或者直接查看开发板上的丝印标注。

另外在资料盘(A盘)→3_正点原子领航者ZYNQ开发板原理图文件夹下,有提供 Excel格式的管脚

分配表格,表格里共两个工作表,一个是“PL IO 引脚列表”,另一个是“PS IO 引脚列表”,方便大家查

看。

PS端的 IO分配

在ZYNQ PS端同样也包含了 3个IO BANK,如下图所示:

图 3.1.4 PS 端的 BANK500

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

52

领航者ZYNQ之FPGA 开发指南

图 3.1.5 PS 端的 BANK501

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

53

领航者ZYNQ之FPGA 开发指南

图 3.1.6 PS 端的 BANK502

ZYNQ不同的IO BANK可以采用不同的供电电压, IO BANK的引脚电平和供电电压的电平保持一致,我们根据PS端连接不同的外设来选择不同的供电电压。 BANK500、 BANK501和BANK502分别采用3.3V、1.8V 和1.5V 供电。

与PL 端 IO BANK不同的是,PS端的IO连接是是相对固定的,用户不能够像PL 引脚那样,将PS端

的 IO随意分配到某个外设。PS端外设的IO口与 MIO(多路复用 IO)之间,具有固定关系的映射,某个

外设的 IO口可能会映射到不同的 MIO 上,某个MIO 也有可能会具有多个外设的IO 口映射到其上面。两

者之间的映射如下图所示:

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

54

领航者ZYNQ之FPGA 开发指南

图 3.1.7 PS 端外设和MIO之间的映射

领航者ZYNQ 开发板所使用到的所有外设与 MIO之间所选择的映射关系如下表所示:

表 3.1.2 领航者ZYNQ PS端 IO引脚分配总表

信号名 管脚 端口说明

2个PS功能按键

ps_key[0] MIO12 PS按键KEY0

ps_key[1] MIO11 PS按键KEY1

3个PS_LED灯

ps_led[0](底板) MIO7 PS_LED0

ps_led[1](底板) MIO8 PS_LED1

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

55

领航者ZYNQ之FPGA 开发指南

ps_led(核心板) MIO0 PS_LED

QSPI FLASH

QSPI_CS MIO1 QSPI FLASH的片选,低电平有效

QSPI_SCK MIO6 QSPI FLASH的时钟

QSPI_D0 MIO2 QSPI FLASH的数据位0

QSPI_D1 MIO3 QSPI FLASH的数据位1

QSPI_D2 MIO4 QSPI FLASH的数据位2

QSPI_D3 MIO5 QSPI FLASH的数据位3

PS UART

PS_UART_RXD MIO14 PS UART的接收

PS_UART_TXD MIO15 PS UART的发送

PS 以太网

ETH_TXCK MIO16 PS以太网RGMII接口的TX_CLK

ETH_TXD0 MIO17 PS以太网RGMII接口的TX_D0

ETH_TXD1 MIO18 PS以太网RGMII接口的TX_D1

ETH_TXD2 MIO19 PS以太网RGMII接口的TX_D2

ETH_TXD3 MIO20 PS以太网RGMII接口的TX_D3

ETH_TXCTL MIO21 PS以太网RGMII接口的TX_CTL

ETH_RXCK MIO22 PS以太网RGMII接口的RX_CLK

ETH_RXD0 MIO23 PS以太网RGMII接口的RX_D0

ETH_RXD1 MIO24 PS以太网RGMII接口的RX_D1

ETH_RXD2 MIO25 PS以太网RGMII接口的RX_D2

ETH_RXD3 MIO26 PS以太网RGMII接口的RX_D3

ETH_RXCTL MIO27 PS以太网RGMII接口的RX_CTL

ETH_MDC MIO52 PS以太网MDIO接口的时钟

ETH_MDIO MIO53 PS以太网MDIO接口的数据

PS USB接口

OTG_DIR MIO29 USB总线方向控制

OTG_STP MIO30 数据传输的结束信号

OTG_NXT MIO31 当前数据接收完成指示信号

OTG_CLK MIO36 PHY的时钟输出

OTG_DATA7 MIO39 双向数据总线位7

OTG_DATA6 MIO38 双向数据总线位6

OTG_DATA5 MIO37 双向数据总线位5

OTG_DATA4 MIO28 双向数据总线位4

OTG_DATA3 MIO35 双向数据总线位3

OTG_DATA2 MIO34 双向数据总线位2

OTG_DATA1 MIO33 双向数据总线位1

OTG_DATA0 MIO32 双向数据总线位0

SD卡

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

56

领航者ZYNQ之FPGA 开发指南

SD_CLK MIO40 SD卡的时钟信号

SD_CMD MIO41 SD卡的命令信号

SD_D0 MIO42 SD卡的DATA0

SD_D1 MIO43 SD卡的DATA1

SD_D2 MIO44 SD卡的DATA2

SD_D3 MIO45 SD卡的DATA3

eMMC存储器

eMMC_CCLK MIO48 eMMC的时钟信号

eMMC_CMD MIO47 eMMC的命令信号

eMMC_D0 MIO46 eMMC的DATA0

eMMC_D1 MIO49 eMMC的DATA1

eMMC_D2 MIO50 eMMC的DATA2

eMMC_D3 MIO51 eMMC的DATA3

开发板底板原理图详解

底板电源

底板电源拓扑结构如下图所示:

图 3.2.1 底板电源拓扑

整个板子的电源来自电源适配器的 12V 供电电压,经过DC-DC 芯片(型号为JW50690T_6)之后,转

变为系统+5V 电压,再经过电源开关后,给系统供电,核心板的电源就来自系统+5V 电压。PS端USB 串口

的+5V也可以用来给系统供电,但是需要特别注意,由于USB 接口的驱动能力有限,所以不能驱动供电电

流需求大的器件如LCD, 这种情况下,请改用电源适配器供电。系统+5V电压除了直接驱动某些外设之外,还用于电压转换,LDO(线性稳压器)芯片AMS1117-3.3和AMS1117-1.8用于将系统+5V 电压分别转变为

+3.3V和+1.8V,然后给各个外设供电。

使用+5V 电压供电的底板外设包括ATK MODULE、CAN、RGB LCD 接口、AUDIO、HDMI接口、核

心板、扩展口、USB HUB。使用+3.3V 电压供电的底板外设包括 SP3232、EEPROM、RTC、TOUCH

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

57

领航者ZYNQ之FPGA 开发指南

KEY(AR101)、BEEP、摄像 ......

1

领航者ZYNQ之FPGA 开发指南

领航者 ZYNQ 之 FPGA

开发指南 V1.2.1

-正点原子 领航者 NAVIGATOR 开发板教程

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

2

领航者ZYNQ之FPGA 开发指南

广州市星翼电子科技有限公司

淘宝店铺1:http:eboard.taobao.com

淘宝店铺2:http:openedv.taobao.com

技术支持论坛 (开源电子网) :www.openedv.com

原子哥在线教学:www.yuanzige.com

官方网站:www.alientek.com

最新资料下载链接:http:www.openedv.compostslist13912.htm

E-mail: 389063473@qq.com QQ: 389063473

咨询电话:020-38271790

传真号码:020-36773971

团队:正点原子团队

正点原子,做最全面、最优秀的嵌入式开发平台软硬件供应商。

友 情 提 示

如果您想及时免费获取“正点原子”最新资料,敬请关注正点原子

微信公众平台,我们将及时给您发布最新消息和重要资料。

关注方法:

(1)微信“扫一扫”,扫描右侧二维码,添加关注

(2)微信→添加朋友→公众号→输入“正点原子”→关注

(3)微信→添加朋友→输入“alientek_stm32” →关注

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

3

领航者ZYNQ之FPGA 开发指南

目录

内容简介 .............................................................................. 9

前 言 .............................................................................. 10

第一篇 硬件篇 ................................................................... 11

ZYNQ简介 ................................................................. 12

ZYNQ简介 ..................................................................... 13

FPGA简介 ..................................................................... 15

ZYNQ PL简介 .................................................................. 20

ZYNQ PS简介 .................................................................. 26

实验平台简介 ............................................................. 31

领航者ZYNQ开发板资源初探 ..................................................... 32

领航者开发板底板资源 ................................................... 32

领航者开发板核心板资源 ................................................. 34

领航者ZYNQ开发板资源说明 ..................................................... 36

硬件资源说明 ........................................................... 36

软件资源说明 ........................................................... 42

硬件资源详解 ............................................................. 45

领航者ZYNQ的IO分配 ........................................................... 46

PL端的IO分配 ........................................................... 46

PS端的IO分配 ........................................................... 51

开发板底板原理图详解 ......................................................... 56

底板电源 ............................................................... 56

ZYNQ 启动模式 .......................................................... 59

有源蜂鸣器 ............................................................. 59

PL LED ................................................................. 60

PS LED ................................................................. 60

PL按键 ................................................................. 61

PS按键 ................................................................. 61

电容触摸按键 ........................................................... 62

14-Pin JTAG接口 ........................................................ 63

USB串口 ............................................................... 63

RS232 接口 ............................................................ 64

RS485 接口 ............................................................ 65

RGB LCD 模块接口....................................................... 66

XADC接口 .............................................................. 67

OLED摄像头模块接口 ................................................... 68

EEPROM ................................................................ 68

实时时钟 .............................................................. 69

ATK模块接口 ............................................................ 70

I2S音频编解码 ......................................................... 71

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

4

领航者ZYNQ之FPGA 开发指南

HDMI接口 .............................................................. 72

PL端千兆以太网接口(RJ45) ............................................. 74

USB 2.0接口 ........................................................... 76

Micro SD卡接口 ........................................................ 79

CAN接口 ............................................................... 80

IO扩展口 .............................................................. 81

开发板核心板原理图详解 ....................................................... 82

核心板电源 ............................................................. 82

ZYNQ主控芯片 ........................................................... 85

DDR3 SDRAM存储器 ....................................................... 88

6-Pin JTAG 接口 ......................................................... 91

PS复位按键 ............................................................. 92

PL LED ................................................................. 92

PS LED ................................................................. 93

PL时钟输入 ............................................................. 93

PS时钟输入 ............................................................. 93

PL配置状态指示灯 ...................................................... 94

PS端千兆以太网 ........................................................ 94

QSPI FLASH ............................................................ 96

eMMC .................................................................. 97

开发板使用注意事项 ........................................................... 98

ZYNQ的学习方法 ............................................................... 99

第二篇 软件篇 .................................................................. 101

Vivado软件的安装和使用 .................................................. 102

Vivado软件的安装 ............................................................ 103

Vivado软件的使用 ............................................................ 112

新建工程 .............................................................. 113

设计输入 .............................................................. 121

分析与综合 ............................................................ 127

约束输入 .............................................................. 131

设计实现 .............................................................. 134

下载比特流 ............................................................ 136

在线逻辑分析仪的使用 ........................................................ 141

HDL实例化调试探针流程.................................................. 142

Hardware Manager中观察调试信号 ......................................... 148

网表插入调试探针流程 .................................................. 153

在Vivado中进行功能仿真 ...................................................... 162

第三篇 语法篇 .................................................................. 178

Verilog HDL语法 ......................................................... 179

Verilog概述 ................................................................. 180

Verilog简介 ........................................................... 180

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

5

领航者ZYNQ之FPGA 开发指南

为什么需要Verilog ..................................................... 180

Verilog和VHDL区别 ..................................................... 180

Verilog和C的区别 ...................................................... 181

Verilog基础知识 ............................................................. 181

Verilog的逻辑值 ....................................................... 181

Verilog的标识符 ....................................................... 182

Verilog的数字进制格式.................................................. 182

Verilog的数据类型 ..................................................... 182

Verilog的运算符 ....................................................... 183

Verilog程序框架 ............................................................. 186

注释 .................................................................. 186

关键字 ................................................................ 186

程序框架 .............................................................. 187

Verilog高级知识点 ........................................................... 190

阻塞赋值(Blocking)................................................... 190

非阻塞赋值(Non-Blocking) ............................................. 191

assign和always区别 .................................................... 193

带时钟和不带时钟的always............................................... 193

什么是latch ........................................................... 194

状态机 ................................................................ 195

模块化设计 ............................................................ 199

Verilog编程规范 ............................................................. 203

编程规范重要性 ........................................................ 203

工程组织形式 .......................................................... 204

文件头声明 ............................................................ 204

输入输出定义 .......................................................... 205

parameter定义 ......................................................... 205

wirereg定义 .......................................................... 205

信号命名 .............................................................. 206

always块描述方式 ...................................................... 206

assign块描述方式 ...................................................... 207

空格和TAB ............................................................ 207

注释 ................................................................. 207

模块例化 ............................................................. 208

其他注意事项 ......................................................... 208

第四篇 实战篇 .................................................................. 210

LED灯闪烁实验 ........................................................... 211

LED灯简介 ................................................................... 212

实验任务 .................................................................... 212

硬件设计 .................................................................... 212

程序设计 .................................................................... 213

原子哥在线教学:www.yuanzige.com 论坛:www.openedv.com

6

领航者ZYNQ之FPGA 开发指南

下载验证 .................................................................... 216

按键控制LED闪烁实验 ..................................................... 219

按键简介 .................................................................... 220

实验任务 .................................................................... 220

硬件设计 .................................................................... 220

程序设计 .................................................................... 221

下载验证 .................................................................... 223

按键控制蜂鸣器实验 ...................................................... 224

蜂鸣器简介 .................................................................. 225

实验任务 .................................................................... 225

硬件设计 .................................................................... 225

程序设计 .................................................................... 226

下载验证 .................................................................... 230

触摸按键控制LED灯实验 ................................................... 231

触摸按键简介 ................................................................ 232

实验任务 .................................................................... 232

硬件设计 .................................................................... 232

程序设计 .................................................................... 233

下载验证 .................................................................... 236

呼吸灯实验 .............................................................. 238

呼吸灯简介 ................................................................. 239

实验任务 ................................................................... 239

硬件设计 ................................................................... 239

程序设计 ................................................................... 240

下载验证 ................................................................... 242

IP核之MMCMPLL实验 ...................................................... 243

MMCMPLL IP核简介 .......................................................... 244

实验任务 ................................................................... 247

硬件设计 ................................................................... 247

程序设计 ................................................................... 248

下载验证 ................................................................... 255

IP核之RAM实验 ........................................................... 257

RAM IP核简介 ............................................................... 258

实验任务 ................................................................... 259

硬件设计 ................................................................... 259

程序设计 ................................................................... 259

下载验证 ................................................................... 267